# EXTENSIBLE MESSAGE LAYERS FOR RESOURCE-RICH CLUSTER COMPUTERS

A Dissertation

Presented to

The Academic Faculty

By

Craig D. Ulmer

In Partial Fulfillment

Of the Requirements for the Degree

Doctor of Philosophy in Electrical and Computer Engineering

Georgia Institute of Technology

November 2002

Copyright © 2002 Craig D. Ulmer

# Extensible Message Layers for Resource-Rich Cluster Computers

| Approved:    |             |               |

|--------------|-------------|---------------|

| Dr. Sudhaka  | r Yalamanch | ıili, Advisor |

| Ør. Kenneth  | Mackenzie   |               |

| Dr. David So | chimmel     |               |

| Date Approv  | ved. 11/19  | 1d002         |

For my parents, Steve and Judy Ulmer, and especially my patient and loving wife, Amy.

#### **FOREWORD**

Approximately five years ago, Dr. Yalamanchili asked me if I would be interested in working with NASA to develop the computational systems for the next generation of spaceborne vehicles. The Remote Exploration and Engineering (REE) project at NASA had just finished a report concluding that future unmanned exploration vehicles would have to operate autonomously in order to be successful. These systems would have to capture large amounts of scientific data, process it locally, and transmit the most significant information back to Earth. In order to reduce development costs, NASA was interested in employing cluster computers in the spaceborne vehicles to perform these computational evaluations. My contribution to this effort would be to construct communication software that allows data to flow in a reliable and efficient manner between the hardware components of the system. Being that cluster computers are normally tucked away in the unwanted closets of a research building, it was appealing to think that we would be setting a few free, to be clusters in the sky. Aware of how this sounded similar to a Star Trek movie, I jumped at the opportunity.

After three years of work, we had constructed a functional communication library that achieved the goals of the research project. In addition to implementing the functionality commonly found in other communication libraries, our software allowed an intelligent server adaptor card to interact directly with the network interface. Plus, it had a cool name: GRIM (to which my advisor is still rolls his eyes). After the initial release of GRIM, we began investigating how the software could be improved to support other peripheral devices. As this work evolved, we realized that we were really providing a new form of cluster architecture. We refer to these clusters as resource-rich cluster computers, which are the focus of this dissertation.

As fate would have it, a number of researchers in industry were working on similar problems for commercial network servers. Their effort resulted in the InfiniBand I/O standard. Being that multimillion-dollar companies backed InfiniBand, we were initially concerned that we would be swept away by this monumental effort. However, we continued on with our work, following in the do-it-yourself style that has been the basis of the cluster computing movement. Our effort was rewarded earlier this year, when an InfiniBand evangelist stated in a keynote speech that the true threat to InfiniBand was from grassroots efforts taking place in commodity networks such as Gigabit Ethernet. Being that GRIM is designed to be applicable to any network substrate with intelligent network interface cards (including Gigabit Ethernet), we recognize this as a small victory and an indication that our effort has been worthwhile.

There are many organizations and people that have had a significant and positive impact on this research. This work was financially supported through a fellowship from NASA's Jet Propulsion Laboratory as well as through grants from the National Science Foundation. The cluster computer hardware utilized in this research was funded through large donations by the Intel Corporation. This work certainly would not have been feasible without these contributions, and we gratefully acknowledge the financial support of these organizations.

There are a number of professors that have had a significant influence on this work. First and foremost, this work would not have been possible without the assistance of my advisor, Dr. Sudhakar Yalamanchili. Sudha has been a constant source of encouragement and guidance over the years. Our weekly meetings always motivated me to push a little harder, and to construct new functionality that was beyond our original goals. Sudha helped transform a large amount of my text into actual (and concise) English. He did this in a kind way, often suggesting that he only had to make "a few minor changes" to something that I knew was poorly written. I am grateful for all the help and counseling Sudha has given me over the years. I will truly miss our whiteboard-centered meetings, where everything needed a block diagram no matter how irrelevant it was.

Dr. Kenneth Mackenzie also provided a great deal of assistance in this work. Ken's keen eye for detail motivated me to take a closer look into the low-level performance characteristics of the hardware. Ken continually surprised me by answering my questions with real performance measurements from programs he cooked up on the spot. Without his obsession for optimality, GRIM would never have reached its current level of performance. Ken was kind enough to allow me to use his cluster, even when he knew that I have a tendency to disorganize or break things. Most importantly, Ken instantly saw the soul of my work and enlisted me in the crusade to turn modern, boring computer architecture on its head. I can only hope that Ken will continue the good fight, and not get tied down by the bureaucracy.

Other professors had a significant impact on this work. Dr. Leon Alkalai provided encouragement and summer internships at NASA JPL. Leon supplied me with valuable view of the internals of JPL's work, and helped open my eyes to solving larger problems than what my degree had prepared me for. Dr. José Duato also assisted me in this work over the years. While only briefly mentioned in this dissertation, the discussions of deadlock freedom in irregular network topologies that took place with José, Sudha, and myself are part of the work that I enjoyed the most in graduate school.

I am fortunate to have been surrounded by many high-quality researchers and co-workers as a graduate student at Georgia Tech. Early on, Darrell Stogner, Santiago Abraham, and Phivu Nguyen provided me with a drive to investigate new technical material. Emily Crawford performed the initial backbreaking work with the Myrinet hardware that served as a starting point for my work. Ivan Ganev meticulously answered my kernel questions, no matter how silly they were. His shaved head also took Ken's attention away from my infrequent, self-induced buzz cuts. William Norton, Damon Love, and John Lockhart supplied me with a constant stream of desirable distractions, and served as a reality check for my work. I frequently harassed these people with painful implementation problems ("I just shifted all of a host's physical memory by 1024 bytes"). Thanks for frequently coming out to the Original Pancake House to listen and

provide useful suggestions ("Try not to do that"). Finally, Amer Abufadel has been a constant source of knowledge and help. In addition to answering my DSP questions, Amer and I went

through many of the graduate student anxieties at the same time.

This work would not have been possible without the support of my family. My brother, Dr. Todd Ulmer, constantly pressed me to push on and finish. He also wrote a wonderful "forward" in his own dissertation that has made it impossible for me to write a halfway decent one myself. In any case, when I was young, Todd teased me by throwing my favorite toy, a little red plastic hammer, out the widow of our dad's moving car. While I will hold that over his head forever, he should know he is a good older brother and I thank him for all the help he has given me in school. I would also like to thank my parents for their love and support over the years. Even though they never quite understood what exactly it was I was working on, they always encouraged me to try harder. Hopefully, this dissertation unravels the mystery of my work a little bit.

Finally, I must thank my wife, Amy Pomerance, for her love and support. Amy patiently waited for me to finish, never letting on that she did not believe me when I kept telling her that it would "only be about a year now". While all of this work seemed to take forever, being with you during this time made it all fine. Thanks for everything.

CRAIG ULMER

NOVEMBER 2002

# TABLE OF CONTENTS

| FOREWORD                                                           | IV    |

|--------------------------------------------------------------------|-------|

| TABLE OF CONTENTS                                                  | viii  |

| LIST OF TABLES                                                     | XIII  |

| LIST OF FIGURES                                                    | XIV   |

| LIST OF ACRONYMS                                                   | XVIII |

| SUMMARY                                                            | XX    |

| CHAPTER 1: INTRODUCTION                                            | 1     |

| 1.1 BACKGROUND                                                     |       |

| 1.2 RESOURCE-RICH CLUSTER COMPUTERS                                | 2     |

| 1.3 CONTRIBUTIONS                                                  |       |

| 1.4 Organization of the Thesis                                     | 5     |

| CHAPTER 2: BACKGROUND                                              | 7     |

| 2.1 EVOLUTION OF HIGH-PERFORMANCE COMPUTING PLATFORMS              | 8     |

| 2.1.1 A Brief History of Commercial Supercomputers                 | 8     |

| 2.1.2 Motivation for Alternate Computing Platforms                 |       |

| 2.1.3 Emergence of Cluster Computers                               |       |

| 2.2 Using Workstations as a Cluster Computer's Processing Elements | 13    |

| 2.2.1 Workstation CPUs                                             | 14    |

| 2.2.2 Evolution of Workstation I/O Systems                         | 14    |

| 2.2.3 Peripheral Component Interconnect (PCI)                      |       |

| 2.2.4 Architecture Tradeoffs                                       |       |

| 2.3 CLUSTER COMPUTER NETWORK HARDWARE                              | 17    |

| 2.3.1 Ethernet                                                     |       |

| 2.3.2 Scalable Coherent Interconnect (SCI)                         |       |

| 2.3.3 Myrinet                                                      |       |

| 2.3.4 Quadrics QsNet                                               |       |

| 2.4 Cluster Computer Network Software                              |       |

| 2.4.1 Limitations of LAN Protocols                                 |       |

| 2.4.2 Message Layer Characteristics                                |       |

| 2.4.3 Common Message Layer Optimizations                           |       |

| 2.4.4 Myrinet Message Layers                                       |       |

| 2.5 THE VIRTUAL PARALLEL-PROCESSING MACHINE                        | 27    |

| CHAPTER 3: MESSAGE LAYERS FOR RESOURCE-RICH CLUSTER COMPUTER       | RS29  |

| 3.1 EMERGENCE OF RESOURCE-RICH CLUSTER COMPUTERS                   | 30    |

| 3.1.1 Availability of Powerful Peripheral Devices                  | 30    |

| 3.1.2 Categorizing Peripheral Devices                              |       |

| 3.1.3 Characteristics of Resource-Rich Cluster Computer Hardware   |       |

| 3.1.4 Resource-Rich Cluster Computer Applications                  |       |

| 3.2 DESIGN OF MESSAGE LAYERS FOR RESOURCE-RICH CLUSTERS            |       |

| 3.2.1 Definition of a Communication Endpoint                       |       |

| 3.2.2 Architectural Design Issues                                  | 38    |

| 3.2.3   | Design Overview.                                                                                                        | 39  |

|---------|-------------------------------------------------------------------------------------------------------------------------|-----|

| 3.3     | PER-HOP FLOW CONTROL                                                                                                    |     |

| 3.3.1   | Disadvantages of Endpoint-Managed Flow Control                                                                          | 41  |

| 3.3.2   |                                                                                                                         |     |

| 3.3.3   |                                                                                                                         | 43  |

| 3.4     | LOGICAL CHANNELS                                                                                                        |     |

| 3.4.1   |                                                                                                                         |     |

| 3.4.2   |                                                                                                                         |     |

| 3.4.2   |                                                                                                                         |     |

| 3.5     | ACTIVE MESSAGE PROGRAMMING INTERFACE                                                                                    |     |

| 3.5.1   |                                                                                                                         |     |

| 3.5.2   |                                                                                                                         |     |

| 3.6     | REMOTE MEMORY PROGRAMMING INTERFACE                                                                                     |     |

| 3.6.1   |                                                                                                                         |     |

| 3.6.2   |                                                                                                                         |     |

|         | Remote Memory Interface                                                                                                 |     |

| 3.7     |                                                                                                                         |     |

| 3.7.1   |                                                                                                                         |     |

| 3.7.2   |                                                                                                                         |     |

| 3.7.3   |                                                                                                                         |     |

| 3.7.4   | WINDOWS AND                                                                         |     |

| CHAPTEI | R 4: MESSAGE LAYER IMPLEMENTATION: GRIM                                                                                 | 59  |

| 4.1     | OVERVIEW OF GRIM                                                                                                        | 59  |

| 4.1.1   | Message Structure                                                                                                       | 61  |

| 4.2     | NI-BASED RELIABLE TRANSMISSION PROTOCOL                                                                                 | 64  |

| 4.2.1   | Protocol                                                                                                                | 64  |

| 4.2.2   |                                                                                                                         |     |

| 4.2.3   |                                                                                                                         |     |

| 4.2.4   |                                                                                                                         |     |

| 4.3     | LOGICAL CHANNELS                                                                                                        | 72  |

| 4.3.1   | Logical Channel Structure                                                                                               | 73  |

| 4.3.2   | Message Sequencing with Multiple Logical Channels                                                                       |     |

| 4.3.3   |                                                                                                                         |     |

| 4.3.4   |                                                                                                                         |     |

| 4.4     | ACTIVE MESSAGE INTERFACE                                                                                                |     |

| 4.4.1   |                                                                                                                         |     |

| 4.4.2   |                                                                                                                         |     |

| 4.4.3   | 는 사람들이 있다고 <b>~~</b> 사용 기업으로 하는 것으로 함께 가는 것으로 함께 있는 이렇지 않는 사람들이 되었다. 그런 사람들이 가는 사람들이 되었다면 하는 것을 하는 것이다면 하는데 없다면 하는데 있다. |     |

| 4.5     | REMOTE MEMORY INTERFACE                                                                                                 |     |

| 4.5.1   | Registered Memory                                                                                                       |     |

| 4.5.2   | Virtual Memory Translation in the NI                                                                                    |     |

| 4.5.3   | 그 마다 사람들은 아니는                                                                       |     |

| 4.5.4   |                                                                                                                         |     |

| 4.5.5   | Endpoint Notification for Remote Memory Operations                                                                      |     |

| 4.5.6   |                                                                                                                         |     |

| 4.6     | SUMMARY                                                                                                                 |     |

| 1811273 |                                                                                                                         |     |

| CHAPTEI | R 5: HOST-TO-HOST TRANSFERS                                                                                             |     |

| 5.1     | OVERVIEW OF THE HOST-TO-HOST COMMUNICATION PATH                                                                         |     |

| 5.1.1   |                                                                                                                         |     |

| 5.2     | INJECTING DATA INTO THE SENDING NI (HOST-NI)                                                                            |     |

| 5.2.1   | Programmed I/O Transfer Mechanisms                                                                                      |     |

| 5.2.2   |                                                                                                                         |     |

| 5.2.3   | TPIL Host-to-NI Performance.                                                                                            |     |

| 5.3     | DATA TRANSFER BETWEEN NI PAIRS (NI-NI)                                                                                  |     |

| 5.3.1   | Native SAN Performance                                                                                                  | 101 |

|    | 5.3.2   | Overhead for the Sending and Receiving NIs                  |     |

|----|---------|-------------------------------------------------------------|-----|

|    | 5.4     | EJECTING DATA FROM THE RECEIVING NI (NI-HOST)               | 103 |

|    | 5.4.1   | Native NI PCI Performance                                   | 104 |

|    | 5.4.2   | Active Message Delivery                                     | 105 |

|    | 5.4.3   | Remote Memory Execution                                     |     |

|    |         | PERFORMANCE AND OPTIMIZATIONS OF THE COMMUNICATION PATH     |     |

|    | 5.5.1   | Store-and-Forward Communication Model                       |     |

|    | 5.5.2   | Store-and-Forward Pipelining                                |     |

|    | 5.5.3   | Pipelined Store-and-Forward Performance                     |     |

|    |         | Cut-through Optimizations                                   |     |

|    | 5.5.4   |                                                             |     |

|    | 5.5.5   | Performance with Cut-through Optimizations                  |     |

|    |         | OVERALL PERFORMANCE                                         |     |

|    |         | COMPARISON WITH OTHER MESSAGE LAYERS                        |     |

|    | 5.7.1   | Reported Performance                                        |     |

|    | 5.7.2   | Measured Performance                                        | 122 |

| Cl | HAPTER  | t 6: PERIPHERAL DEVICE EXTENSIONS                           | 123 |

|    | 6.1     | ADAPTING A PERIPHERAL DEVICE FOR USE WITH GRIM              | 124 |

|    | 6.1.1   | Peripheral Device Endpoint Software                         |     |

|    |         |                                                             |     |

|    | 6.1.2   | Host-Level Integration                                      |     |

|    | 6.1.3   | Library Initialization                                      |     |

|    | 6.1.4   | Runtime Management                                          |     |

|    |         | CYCLONE MICROSYSTEMS SERVER ADAPTOR CARD                    |     |

|    | 6.2.1   | Endpoint Construction                                       |     |

|    | 6.2.2   | Performance Measurements                                    |     |

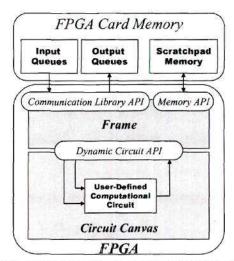

|    | 6.3     | FPGA Accelerator                                            |     |

|    | 6.3.1   | FPGA Overview                                               |     |

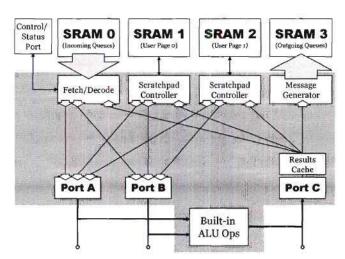

|    | 6.3.2   | Celoxica RC-1000 FPGA Card                                  | 134 |

|    | 6.3.3   | FPGA Endpoint Implementation                                |     |

|    | 6.3.4   | User-Defined Circuits                                       |     |

|    | 6.3.5   | Examples of User-Defined Circuits                           | 138 |

|    | 6.3.6   | RC-1000 Interactions with GRIM                              | 139 |

|    | 6.3.7   | TPIL Performance for the RC-1000 Card                       | 141 |

|    | 6.4     | BROOKTREE VIDEO CAPTURE CARD                                |     |

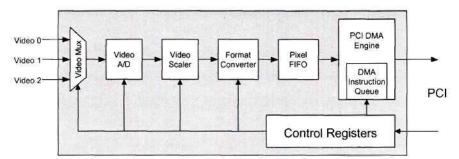

|    | 6.4.1   | Overview of the BT8x8 Video Capture Card                    | 143 |

|    | 6.4.2   | Endpoint Construction.                                      |     |

|    | 6.4.3   | Driver Modifications                                        |     |

|    |         | VIDEO DISPLAY CARDS                                         |     |

|    | 6.5.1   | Video Display Card Overview                                 |     |

|    | 6.5.2   | GRIM Integration                                            |     |

|    | 55.55   | SUMMARY                                                     |     |

|    | (6. 15) |                                                             |     |

| CI | HAPTER  | 7: STREAMING COMPUTATIONS                                   | 150 |

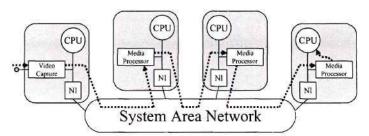

|    | 7.1     | AN OVERVIEW OF STREAMING COMPUTATIONS                       | 151 |

|    | 7.1.1   | Connection-Oriented Streaming Computations                  | 152 |

|    | 7.1.2   | An FPGA-Based Pipeline Unit                                 |     |

|    | 7.2     | PIPELINE COMPUTATIONS                                       |     |

|    | 7.2.1   | The Use of Active Messages to Control Pipeline Computations |     |

|    | 7.2.2   | Dynamic FPGA Circuit Management                             |     |

|    | 7.2.3   | Function Faults in the FPGA Frame                           |     |

|    | 7.2.4   | Function Fault Overhead                                     |     |

|    |         | PIPELINE FORWARDING                                         |     |

|    | 7.3.1   | Forwarding                                                  |     |

|    | 7.3.1   | Forwarding Directory                                        |     |

|    | 7.3.2   | FPGA Implementation                                         |     |

|    |         | MANAGING PIPELINE STATE INFORMATION                         |     |

|    | 7.4     | IVIANACING FIFELINE STATE INFORMATION                       | 101 |

| 7.4.1   | Managing On-Card Memory for an Endpoint                |     |

|---------|--------------------------------------------------------|-----|

| 7.4.2   | Virtual Memory for the RC-1000 FPGA Endpoint           | 163 |

| 7.4.3   | Page Fault Performance                                 |     |

| 7.5     | PERFORMANCE OF AN FPGA AS A PIPELINE STAGE             | 166 |

| 7.6     | Summary                                                |     |

|         |                                                        |     |

| CHAPTER | 8 8: MESSAGE LAYER EXTENSIONS                          | 169 |

| 8.1     | MULTICAST                                              | 170 |

| 8.1.1   | Multicast through NI Recycling                         | 171 |

| 8.1.2   | Deadlock Issues in NI-Recycling Multicast              | 173 |

| 8.1.3   | Multicast with a Single Recycle Queue                  | 175 |

| 8.1.4   | Implementation                                         |     |

| 8.1.5   | Multicast Group Updates                                |     |

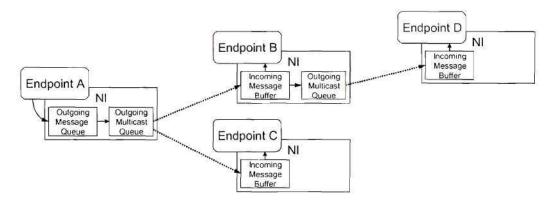

| 8.1.6   | Multicast Communication Path                           |     |

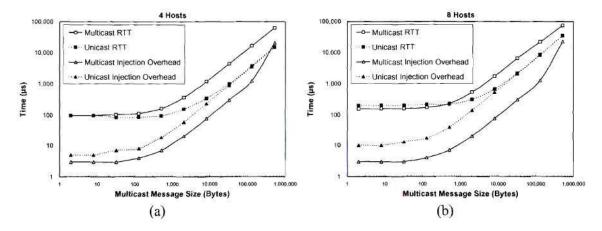

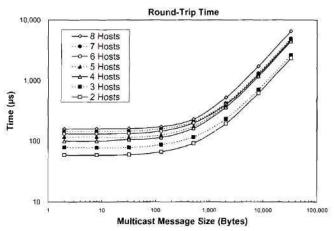

| 8.1.7   | Multicast Performance                                  |     |

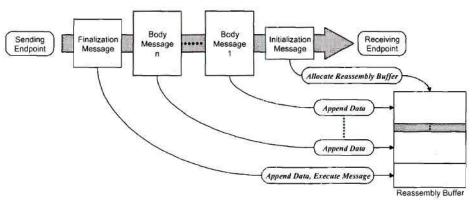

| 8.2     | MESSAGE FRAGMENTATION AND REASSEMBLY MECHANISMS        |     |

| 8.2.1   | Active Message Fragmentation in GRIM                   |     |

| 8.2.2   | Remote Memory Message Fragmentation                    |     |

| 8.2.3   | Multicast Message Fragmentation                        |     |

|         | PROTOCOL EMULATION: A SOCKETS INTERFACE                |     |

| 8.3.1   | Sockets                                                |     |

| 8.3.2   | Planning a Reliable Sockets Emulation.                 |     |

| 8.3.3   | Implementation of a Reliable Sockets Emulation         |     |

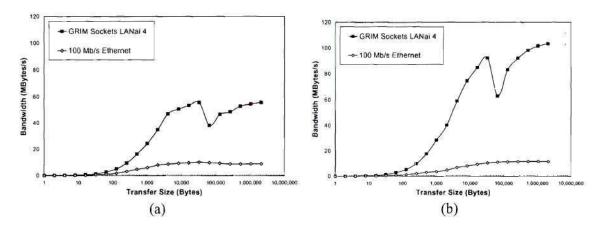

| 8.3.4   | Performance                                            |     |

|         |                                                        |     |

| CHAPTER | R 9: CONCLUSION                                        | 193 |

| 9.1     | IMPLEMENTATION CHALLENGES                              | 195 |

| 9.2     | FUTURE DIRECTIONS                                      | 197 |

| 9.2.1   | GRIM Enhancements                                      | 197 |

| 9.2.2   | Gigabit Ethernet Substrates                            | 198 |

| 9.2.3   | Active SANs                                            | 199 |

| ADDENDI | X A: SUMMARY OF MYRINET NI PERFORMANCE CHARACTERISTICS | 200 |

|         |                                                        |     |

| APPENDI | X B: THE FPGA FRAME API                                | 201 |

| B.1     | ARCHITECTURE OVERVIEW                                  | 202 |

| B.1.1   | Data Path of the Frame                                 | 202 |

| B.2     | COMMUNICATION LIBRARY INTERFACE                        | 204 |

| B.2.1   |                                                        |     |

| B.2.2   | Message Queues                                         |     |

| B.2.3   |                                                        |     |

| B.2.4   |                                                        |     |

| B.2.5   |                                                        |     |

| B.3     | COMPUTATIONAL CIRCUIT INTERFACE                        |     |

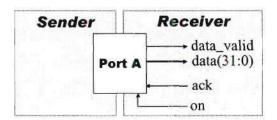

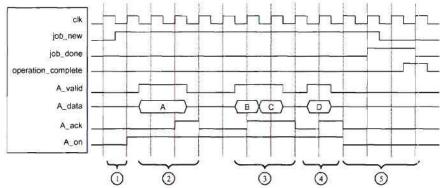

| B.3.1   | Vector Data Port Signaling.                            |     |

| B.3.2   |                                                        |     |

| B.3.3   |                                                        |     |

|         | SCRATCHPAD MEMORY INTERFACE.                           |     |

| B.4.1   | Supplying and Sinking Circuit Data                     |     |

| B.4.2   |                                                        |     |

| B.4.3   |                                                        |     |

|         | GRIM FUNCTION CALLS                                    |     |

| B.6     | DEBUGGING INFRASTRUCTURE                               |     |

| B.6.1   | Simulation Environment                                 |     |

| B.6.2   |                                                        |     |

|         | Future Frame Work                                      |     |

| B.7.1    | Enhancements to the RC-1000 Frame        | 223 |

|----------|------------------------------------------|-----|

| B.7.2    | Future Work with Other FPGA Cards        | 225 |

| APPENDIX | C: THE GRIM API                          | 227 |

| C.1      | CONFIGURATION INTERFACE                  | 227 |

| C.1.1    | Application Configuration                | 228 |

| C.1.2    | Cluster Resource Configurations          |     |

| C.2      | INITIALIZATION: GRIM_ENABLE()            |     |

|          | RUNTIME INFORMATION                      |     |

| C.3.1    | Referencing a Cluster Resource           | 233 |

| C.4      | ACTIVE MESSAGE INTERFACE                 | 233 |

| C.4.1    | Handler Registration                     | 234 |

| C.4.2    | Send and Receive Operations              |     |

| C.5      | REMOTE MEMORY INTERFACE                  |     |

| C.5.1    | Managing Memory                          | 236 |

| C.5.2    | Remote Memory Operations                 |     |

| C.5.3    | Reserving NI Memory                      |     |

| C.6      | MULTICAST                                | 239 |

| C.6.1    | Multicast Tree Management                | 239 |

| C.6.2    | Sending Multicast and Broadcast Messages |     |

| C.7      | ADVANCED API FUNCTIONS: TPIL             |     |

| REFEREN  | CES                                      | 243 |

# LIST OF TABLES

| Table 2.1: A history of Myrinet network interface cards.                                    | 20  |

|---------------------------------------------------------------------------------------------|-----|

| Table 5.1: Reliably delivering a message incurs overhead at the sending and receiving       | ŗ   |

| NIs                                                                                         |     |

| Table 5.2: The amount of time required for the receiving NI to deliver an active mess.      | age |

| to the host endpoint for a P3-550 MHz host                                                  | 106 |

| Table 5.3: The amount of time required for the receiving NI to process a remote mem         | ory |

| operation in a P3-550 MHz host.                                                             | 107 |

| Table 5.4: The overall performance of GRIM.                                                 | 119 |

| Table 5.5: Performance reported for various Myrinet message layers                          | 121 |

| Table 5.6: Measured performance for GM and GRIM.                                            | 122 |

| Table 6.1: Performance measurements for RC-1000 memory arbitration                          |     |

| Table 6.2: Characteristics of BT8x8 video streams.                                          |     |

| Table 7.1: The amount of time required to manage an FPGA function fault                     | 158 |

| Table 7.2: Overhead for managing an FPGA page fault.                                        |     |

| Table 7.3: RC-1000 overhead involved in processing a 4 KB message                           |     |

| Table 8.1: Comparison of the performance of TCP and GRIM Sockets                            | 191 |

| Table B.1: The data fields in an active message header that control the operation of the    |     |

| frame and the corresponding bit lengths.                                                    |     |

| Table B.2: GRIM API for interactions with the Celoxica RC-1000 card                         |     |

| Table C.1: API for obtaining cluster host information.                                      |     |

| Table C.2: Functions for generating a reference to a communication endpoint                 | 233 |

| <b>Table C.3</b> : The functions utilized to register and reference active message function |     |

| handlers                                                                                    |     |

| Table C.4: The functions for sending and receiving active messages                          |     |

| Table C.5: Function calls for managing memory used by the remote memory interface           |     |

|                                                                                             | 237 |

| Table C.6: Functions for transferring data between an endpoint and a remote endpoin         |     |

|                                                                                             |     |

| Table C.7: Functions for reserving memory in the local NI card.                             |     |

| Table C.8: Functions for managing multicast distributions                                   |     |

| Table C.9: Functions for injecting multicast and broadcast messages.                        |     |

| Table C.10: The TPIL API for accelerating injections of data into a peripheral device       |     |

| from a host CPU                                                                             | 241 |

## LIST OF FIGURES

| Figure 1: The architecture of emerging resource-rich cluster computersxx                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

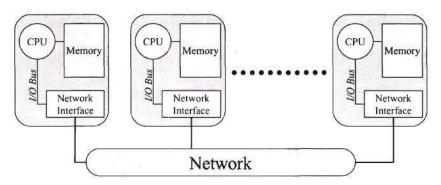

| Figure 2.1: A cluster computer constructed with commodity workstations and network                                                                             |

| hardware12                                                                                                                                                     |

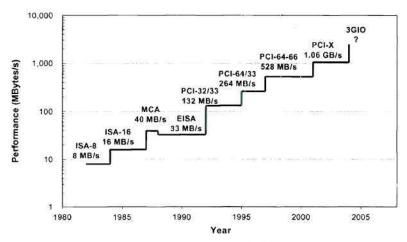

| Figure 2.2: A history of PC I/O systems.                                                                                                                       |

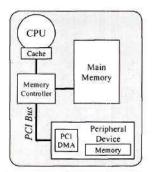

| Figure 2.3: Architecture of a modern host utilizing PCI                                                                                                        |

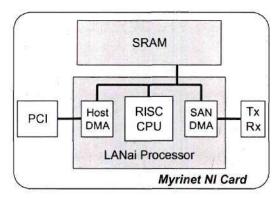

| Figure 2.4: Architecture of the Myrinet NI card. 21                                                                                                            |

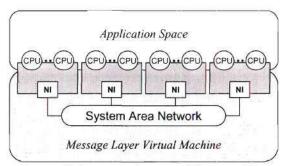

| Figure 2.5: The virtual parallel-processing machine architecture provided to end users in                                                                      |

| current message layers                                                                                                                                         |

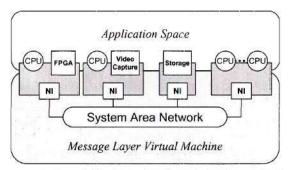

| Figure 3.1: Including peripheral devices in the virtual parallel-processing machine                                                                            |

| architecture provided by the communication library                                                                                                             |

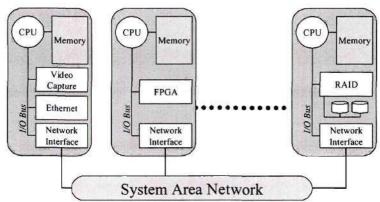

| Figure 3.2: The inclusion of peripheral devices in the resource-rich cluster architecture.                                                                     |

|                                                                                                                                                                |

| Figure 3.3: An example of a resource-rich cluster functioning as a network server 35                                                                           |

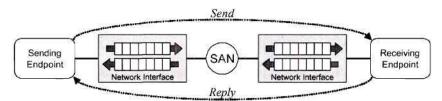

| Figure 3.4: Endpoint-managed flow control schemes typically require send/reply                                                                                 |

| messages to be transferred between endpoints to manage flow control credits. The                                                                               |

| dark buffers in the NIs represent buffer space that is reserved until the send/reply                                                                           |

| transaction completes41                                                                                                                                        |

| Figure 3.5: Per-hop flow control utilizes synchronization in the communication path to                                                                         |

| allow messages to progress when buffer space is available                                                                                                      |

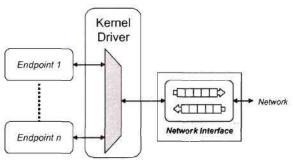

| Figure 3.6: The traditional approach to providing shared access to a network device                                                                            |

| through the use of the kernel                                                                                                                                  |

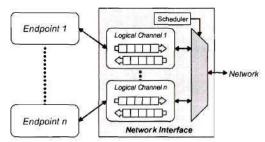

| Figure 3.7: Utilizing multiple logical channels in the NI to provide shared access to the                                                                      |

| network                                                                                                                                                        |

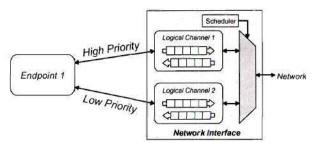

| Figure 3.8: Utilizing multiple logical channels to prioritize messages                                                                                         |

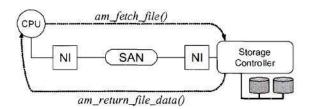

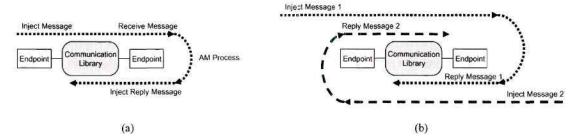

| Figure 3.9: Active messages can be used to facilitate an API for a peripheral device 51                                                                        |

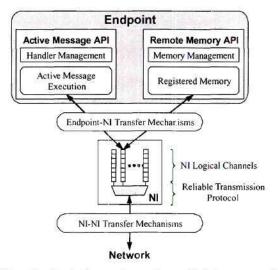

| Figure 4.1: GRIM utilizes logical channels and a reliable transmission protocol at the NI                                                                      |

| and provides two different programming interfaces for end applications                                                                                         |

| Figure 4.2: GRIM uses a single message format for all transactions in the communication                                                                        |

| library                                                                                                                                                        |

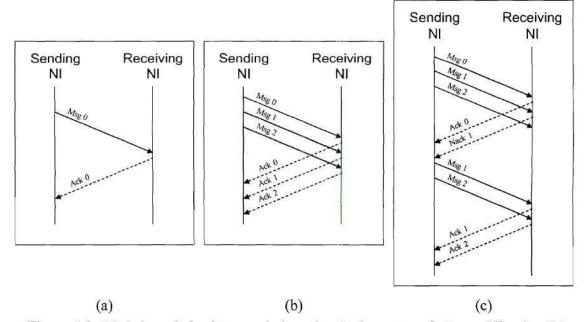

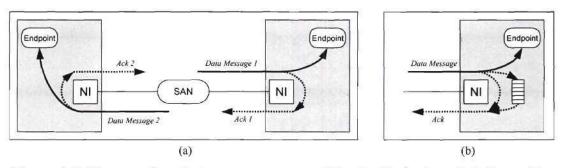

| Figure 4.3: (a) Acknowledged transmission of a single message between NI pairs. (b)                                                                            |

| The optimistic transmission and acknowledgement of three messages. (c) The                                                                                     |

| optimistic transmission of three messages with retransmission due to the lack of                                                                               |

| buffer space. 65                                                                                                                                               |

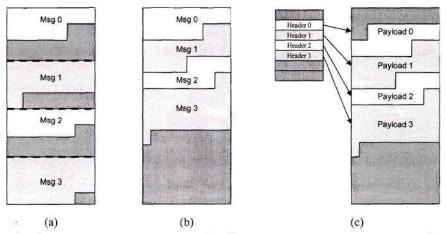

| Figure 4.4: Three approaches to queue buffer management include (a) a fixed-sized slot                                                                         |

| queue buffer, (b) an append-style approach, and (c) a hybrid approach                                                                                          |

| Figure 4.5: The use of control messages can result in deadlock. A cycle is formed in (a)                                                                       |

| when two nodes transmit data messages to each other at the same time. Deadlock                                                                                 |

| can be prevented by buffering control messages (b) when the outgoing link is not                                                                               |

| available                                                                                                                                                      |

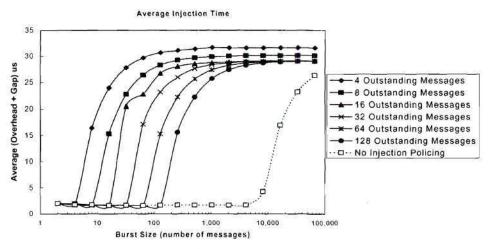

| Figure 4.6: Injection policing effects of a credit-based flow control scheme implemented on top of the optimistic NI-based scheme used in GRIM. Performance is |

| OIL TOD OT THE ODTIFIED INT-DASED SCHEME USED IN CIKTIVI. PERIORMANCE IS                                                                                       |

|        | measured as the average message injection overhead time for null length                  |

|--------|------------------------------------------------------------------------------------------|

|        | messages                                                                                 |

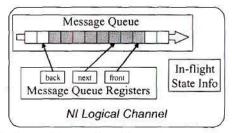

| Figure | 4.7: Each logical channel contains data structures necessary for providing a             |

|        | virtual communication interface                                                          |

| Figure | 4.8: In the any-to-any approach, message sequencing is performed on messages             |

|        | based on the sending and receiving logical channels                                      |

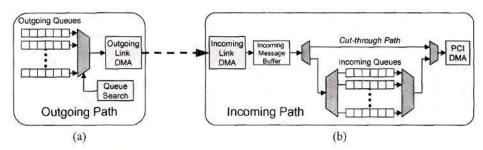

| Figure | 4.9: It is possible to buffer in-flight messages at both the (a) sending NI and the      |

|        | (b) receiving NI. A cut-though path at the receiver improves the performance of          |

|        | the receiving process                                                                    |

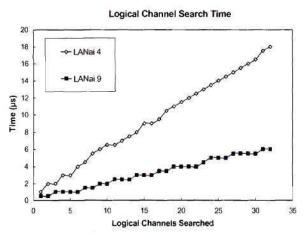

| Figure | 4.10: The amount of time required by the NI to search a fixed number of message          |

| 0      | queues for new messages                                                                  |

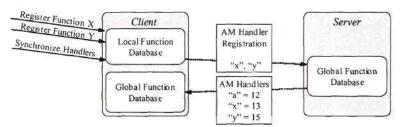

| Figure | 4.11: The active message API requires endpoints to register function handlers            |

|        | locally and then publish the information to a global database                            |

| Figure | 4.12: Example of deadlock at the application level. (a) The dataflow of messages         |

|        | for an active message handler that injects a reply message. (b) Application              |

|        | deadlock due to the simultaneous injection of two messages that require replies.81       |

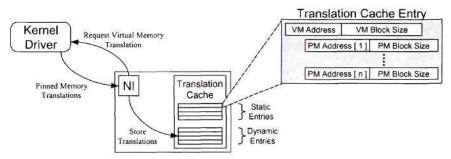

| Figure | 4.13: If a virtual memory translation is not available in the NI's translation cache,    |

|        | the Kernel must be consulted. An entry in the translation cache contains the size        |

|        | of a virtual memory block and a list of its physical memory regions                      |

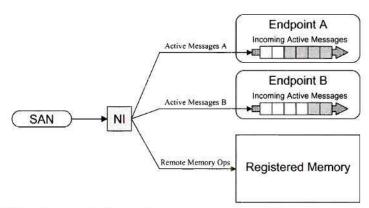

| Figure | 4.14: The data path for active messages provides extra message buffering before          |

| -      | messages are processed compared to the remote memory data path                           |

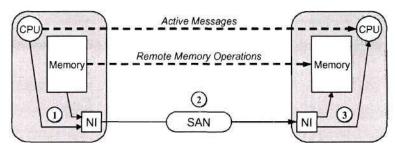

| Figure | 5.1: The active message and remote memory programming interfaces share the               |

|        | same communication path. The three phases of data transfer include (1) Host              |

|        | injection, (2) NI-NI delivery, and (3) NI ejection                                       |

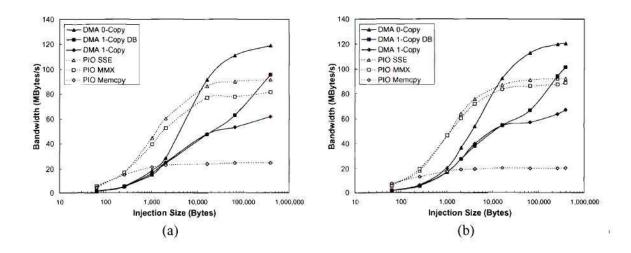

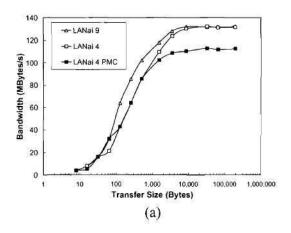

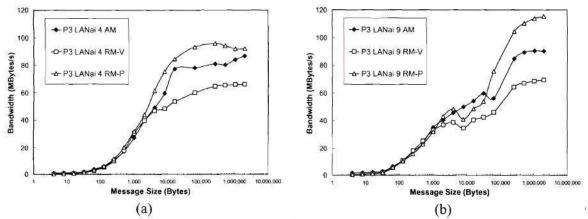

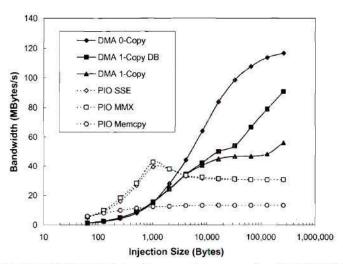

| Figure | 5.2: Host injection performance for a P3-550 MHz host using the (a) LANai 4 and          |

|        | (b) LANai 9 Myrinet NI cards. 98                                                         |

| Figure | 5.3: Host injection performance for a Pentium IV-1.7 GHz using (a) the LANai 4           |

|        | (32b PCI) and (b) the LANai 9 (64b PCI) NI cards                                         |

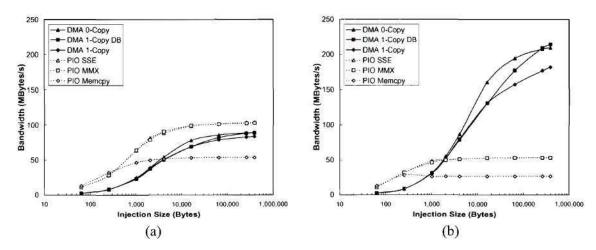

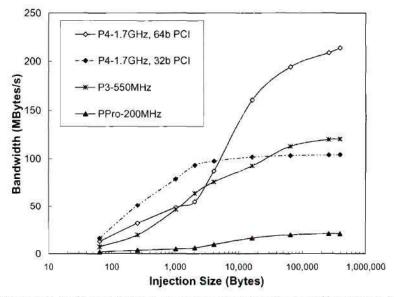

| Figure | 5.4: Overall TPIL performance for three different hosts                                  |

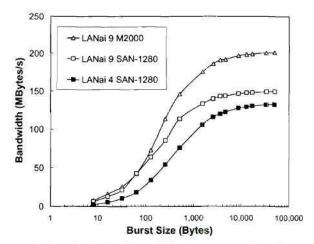

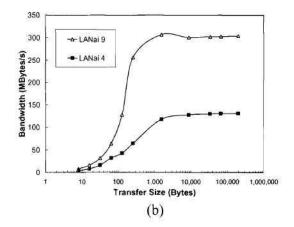

| 200    | 5.5: Observed bandwidth for different transfer sizes between NI pairs.                   |

| -      | Measurements are based on round-trip timings                                             |

| Figure | 5.6: Bandwidth measurements for peripheral device DMA transfers into pinned              |

|        | host memory for (a) P3-550MHz and (b) P4-1.7GHz hosts                                    |

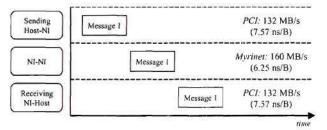

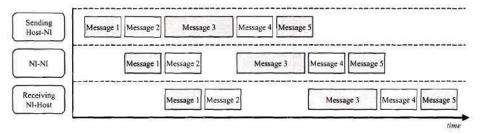

| Figure | 5.7: Messages are moved in their entirety in a store-and-forward communication           |

| 8      | model. The minimum amount of time required to transmit a byte can be                     |

|        | determined by inverting the maximum bandwidth of the transmission mechanism.             |

|        |                                                                                          |

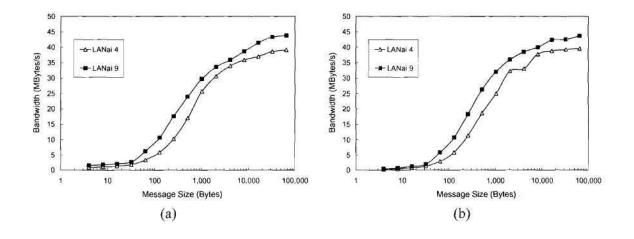

| Figure | 5.8: The store-and-forward performance for a single message transmission                 |

| •      | between a pair of P3-550MHz hosts using (a) active messages and (b) remote               |

|        | memory operations                                                                        |

|        | <b>5.9</b> : Store-and-forward mechanisms can be used to create a communication          |

| 8      | pipeline for increased performance                                                       |

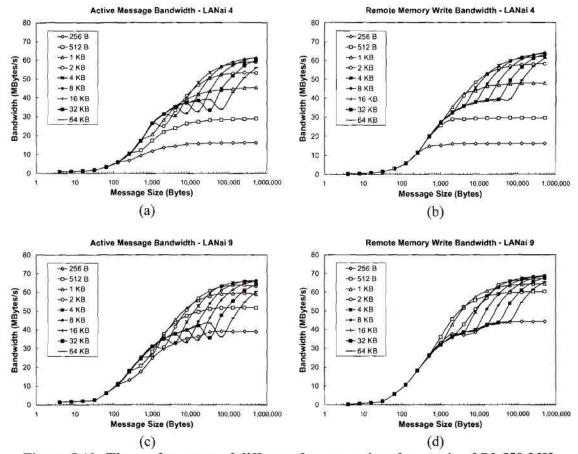

| Figure | <b>5.10</b> : The performance of different fragment sizes for a pair of P3-550 MHz hosts |

|        | using different NIs and different programming interfaces. The tests used (a) active      |

|        | messages with the LANai 4, (b) remote memory operations with the LANai 4, (c)            |

| active messages with the LANai 9, and (d) remote memory operations with the                 |

|---------------------------------------------------------------------------------------------|

| LANai 9                                                                                     |

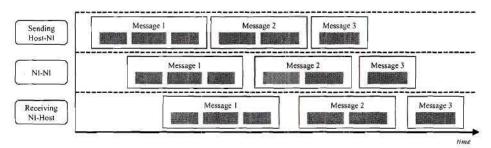

| Figure 5.11: Cut-through optimizations allow a pipeline stage to begin transmitting a       |

| message before all of its data has arrived.                                                 |

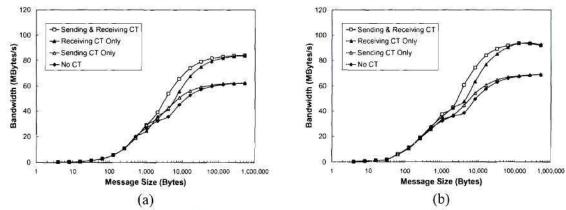

| Figure 5.12: The effects of cut-through optimizations on end-to-end performance             |

| between P3-550MHz hosts using the (a) LANai 4 and (b) LANai 9 NI cards.                     |

| These tests use RM-P programming interface, a fixed cut-through injection size of           |

| 1 KB, and a pipeline fragment size of 4 KB.                                                 |

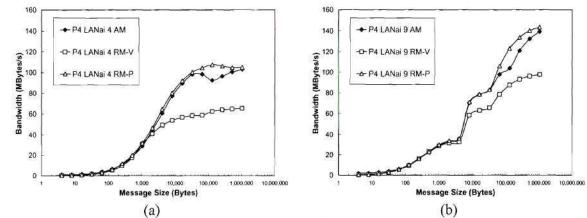

| Figure 5.13: Overall performance of P3-550 MHz hosts in GRIM using (a) LANai 4 and          |

| (b) LANai 9 NI cards                                                                        |

| Figure 5.14: Overall performance of P4-1.7 GHz hosts in GRIM using (a) LANai 4 and          |

| (b) LANai 9 NI cards.                                                                       |

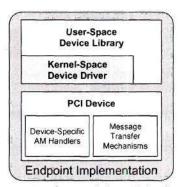

| Figure 6.1: The major components of a peripheral device endpoint implementation 124         |

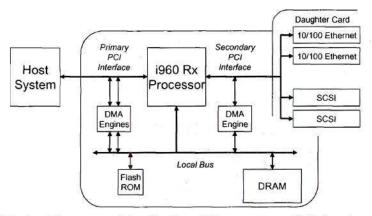

| Figure 6.2: Architecture of the Cyclone Microsystems I <sub>2</sub> O development card      |

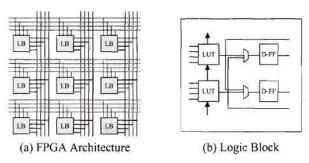

| Figure 6.3: FPGAs are generally (a) large arrays of programmable logic blocks (LBs)         |

| that feature (b) lookup tables (LUTs) and D-flip flops                                      |

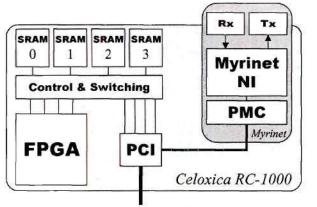

| Figure 6.4: Celoxica RC-1000 and Myrinet Peripheral Devices                                 |

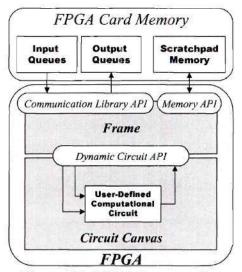

| Figure 6.5: FPGA Organization                                                               |

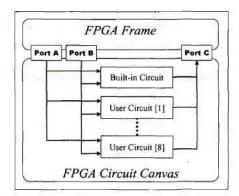

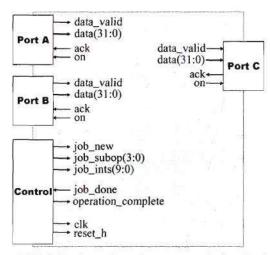

| Figure 6.6: The interface for computational circuits in the canvas                          |

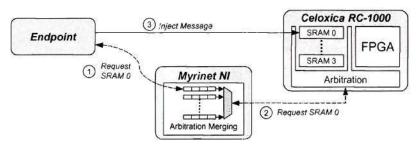

| Figure 6.7: The use of the Myrinet NI to merge arbitration requests. An endpoint (1)        |

| passes a request to the NI to access RC-1000 memory. The NI merges the request              |

| (2) and interacts with the RC-1000 card. After access is granted the endpoint (3)           |

|                                                                                             |

| injects the message                                                                         |

| Figure 6.8: RC-1000 PCI injection performance for P3-550 MHz hosts                          |

| Figure 6.9: The high-level organization of the BT848 chipset                                |

| Figure 7.1: A streaming computation example                                                 |

| Figure 7.2: An example of a connection-oriented streaming computational pipeline 152        |

| Figure 7.3: The process of reconfiguring an FPGA during a function fault                    |

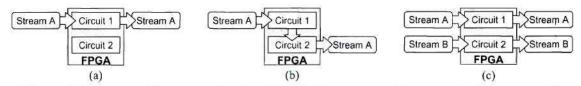

| Figure 7.4: Forwarding examples for (a) a single computation on a single stream, (b)        |

| multiple computations on a single stream, and (c) multiple streams                          |

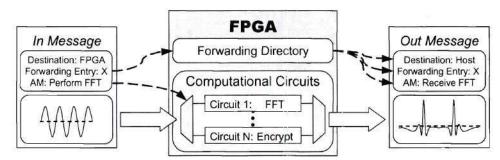

| Figure 7.5: The forwarding directory provides information for transmitting a pipeline       |

| stage's results to another endpoint                                                         |

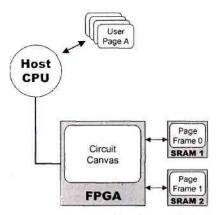

| Figure 7.6: A virtual memory system is implemented for on-card SRAM. SRAM banks 1           |

| and 2 serve as page frames for an application's scratchpad data. Unloaded pages             |

| are swapped into host memory.                                                               |

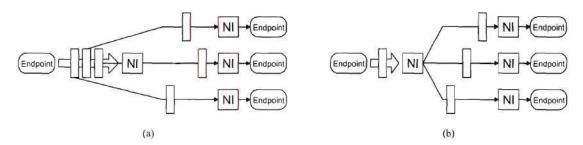

| Figure 8.1: Replicating a multicast message can be performed by (a) the sending             |

| endpoint or (b) in the NI.                                                                  |

| Figure 8.2: The task of replicating messages can be distributed among NIs through (a)       |

| constructing a distribution tree and (b) performing a limited number of multicast           |

| injections at each NI                                                                       |

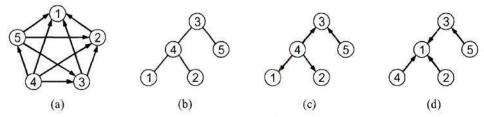

| Figure 8.3: Replicating multicast messages in the NI results in a turn that could lead to a |

| cyclic dependency loop                                                                      |

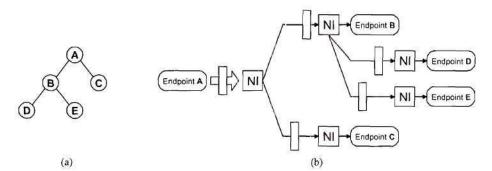

| Figure 8.4: (a) A directed acyclic graph for a cluster's multicast transmissions. (b) A     |

| desired multicast distribution tree. (c) The desired multicast tree when labeled            |

| with link directions. (d) A reordering of the multicast tree that does not violate the      |

| up*/down* routing rules                                                                     |

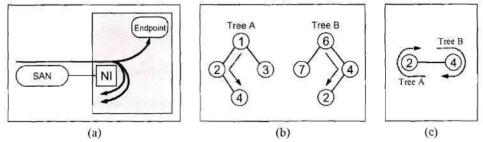

| Figure 8.5: A directed acyclic graph for cluster nodes.                                                                                                | 177 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 8.6: An example of the communication path for a multicast transmission                                                                          |     |

| Figure 8.7: Performance of multicast and unicast messages for (a) 4 and (b) 8 P4-1.7  GHz hosts using LANai 4 NI cards.                                |     |

| Figure 8.8: The measured round-trip times for different sized multicast groups                                                                         | 183 |

| Figure 8.9: Fragmentation and reassembly of a large active message is performed by three types of active message handlers.                             |     |

| Figure 8.10: Performance of the GRIM sockets emulation using LANai 4 NI cards compared to 100 Mb/s Ethernet for (a) P3-550 MHz and (b) P4-1.7 GHz host | ts. |

|                                                                                                                                                        | 191 |

| Figure B.1: The three interfaces managed by the FPGA frame                                                                                             | 202 |

| Figure B.2: The internal structure of the frame for the RC-1000 implementation                                                                         | 203 |

| Figure B.3: The interface between the FPGA's frame and circuit canvas                                                                                  | 210 |

| Figure B.4: The signals for a vector data port                                                                                                         | 210 |

| Figure B.5: The interface for a user-defined circuit                                                                                                   | 212 |

| Figure B.6: An example timing diagram for an asynchronous data vector port                                                                             | 214 |

| Figure B.7: The fields of a scratchpad virtual memory reference.                                                                                       | 218 |

#### LIST OF ACRONYMS

3GIO: Third generation I/O

AGP: Accelerated graphics port

AM: Active messages

API: Application programming interface

ASAN: Active system area network

ASIC: Application-specific integrated circuit BIP: Built-in Parallelism message layer BT8x8: Brooktree video capture card chipset

COTS: Commercial off-the-shelf

CPLD: Complex Programmable Logic Device

CPU: Central processing unit

DMA: Direct memory access

DSM: Distributed shared memory

DSP: Discrete signal processor/processing EISA: Enhanced industry standard architecture

FC: Flow control

FFT: Fast Fourier transform

FM: Fast messages

FPGA: Field-programmable gate array

GM: Glenn's Messages GNU: GNU's not Unix

GRIM: General-purpose Reliable In-order Messages

IB: InfiniBand

IP: Internet Protocol

ISA: Industry standard architecture

LC: Logical channel

LFC: Link-level flow control MCA: Microchannel adaptor

MFLOPS: Millions of floating-point operations per second

MP: Multiprocessor

MPI: Message Passing Interface

MPP: Massively parallel processor

MTU: Maximum transfer unit

NI: Network interface

NIC: Network interface card PC: Personal computer

PCI: Peripheral component interconnect RAID: Redundant array of independent disks

RPC: Remote procedure call

SAN: System area network (also storage area network)

SMP: Symmetric multiprocessor

SRAM: Synchronous RAM

TCP: Transmission control protocol TPIL: Tunable PCI injection library

UDP:

VM:

User datagram protocol Virtual memory Virtual memory mapped communication Virtual node number VMMC:

VNN:

#### SUMMARY

Cluster computing is an alternative approach to supercomputing where a large number of commodity workstations are utilized as the processing elements in a multiprocessor system. These workstations are interconnected by high-performance system area network hardware and specially designed "message layer" communication software. In the current generation of cluster computers, researchers have optimized message layers for communication between the host CPUs in the cluster in order to provide scalable computing performance. However, the recent development of a number of high-performance peripheral devices challenges the notion that message layers should be designed in such a CPU-centric manner. Modern peripheral devices feature powerful embedded processing and storage capabilities that can be leveraged to boost the performance of distributed applications. These peripherals function as sources and sinks of application data, and in some cases, as computational accelerators for offloading host-CPU tasks.

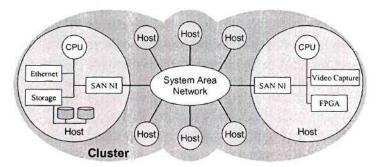

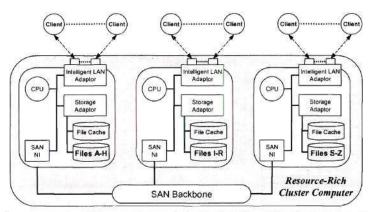

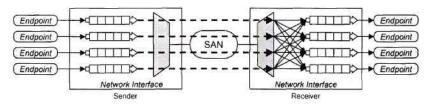

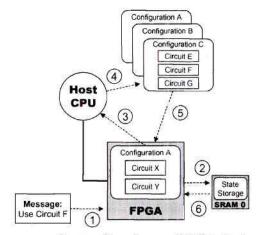

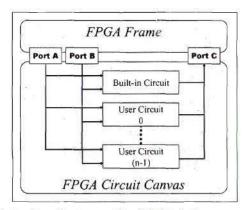

Figure 1: The architecture of emerging resource-rich cluster computers.

As Moore's Law continues its relentless trend, there will continue to be a migration of computing power to peripheral devices. Future clusters will not appear anything like the clusters of today. They will be rich in connectivity and computing power that is deeply embedded in the distributed components of the cluster. We refer to this new generation of systems as *resource-rich cluster computers* (Figure 1). These systems differ from traditional clusters in that application

processing takes place in both the host CPUs and the peripheral devices. While the semiconductor industry continues to alter the economies of scale, the system software that productively enables resource-rich clusters is sorely lagging. Specifically, current generation message layers are ill equipped to service the needs of resource-rich clusters, as they are not designed to utilize peripheral devices as globally accessible resources in a cluster.

This thesis focuses on the challenge of designing extensible message layers for this new generation of resource-rich clusters. We are specifically concerned with making peripheral devices available as globally accessible resources in the context of a programming model that permits applications to effectively and efficiently exploit the capabilities afforded by resource-rich clusters. The key contributions of this thesis fall into two categories. The first includes design concepts and programming abstractions for structuring messages layers to integrate powerful peripheral devices into a globally accessible pool of resources. The second class of contributions is engineering solutions to the challenging problems of effectively and efficiently realizing these design concepts in a manner that tracks the evolution of technology, that is, the continued migration of computing power to distributed resources.

#### CHAPTER I

#### INTRODUCTION

#### 1.1 Background

After years of escalating supercomputer costs, researchers in the early 1990's began investing alternative means by which parallel-processing systems for scientific and military applications could be constructed in a more economical fashion. This work resulted in the field of cluster computing, where a large number of commodity workstations are utilized as the processing elements in a multiprocessor system. These workstations are interconnected by a high-performance communication network and function as part of a single, parallel-processing machine. While cluster computers typically lack the peak performance levels of traditional supercomputers, they provide excellent cost-to-performance ratios that have attracted the attention of many users.

The enabling technology for cluster computers is communication software that is referred to as the cluster's message layer. This software provides a set of message-passing programming abstractions that are utilized to transport data between communication endpoints in the cluster. Early research in cluster computers revealed that end application performance is often sensitive to the latency and bandwidth characteristics of a message layer's implementation. Therefore, a significant amount of research in the late 1990's focused on improving the host-to-host communication performance of a cluster's message layer. This effort has resulted in message layers that are highly optimized for efficiently transferring data between a cluster's host CPUs.

#### 1.2 Resource-Rich Cluster Computers

While current generation message layers have been suitable for a number of parallel applications, the recent development of a number of high-performance peripheral devices challenges the notion that message layers should be designed in such a *CPU-centric* manner. Modern peripheral devices feature powerful embedded processing and storage capabilities that can be leverage to boost the performance of distributed applications. These peripherals function as sources and sinks of application data, and in some cases, as computational accelerators for offloading host-CPU tasks.

As Moore's Law continues its relentless trend, there will continue to be a migration of computing power to peripheral devices. Future clusters will not appear anything like the clusters of today. They will be rich in connectivity and computing power that is deeply embedded in the distributed components of the cluster. We refer to this new generation of systems as *resource-rich cluster computers*. These systems differ from traditional clusters in that application processing takes place in both the host CPUs and the peripheral devices. While the semiconductor industry continues to alter the economies of scale, the system software that productively enables resource-rich clusters is sorely lagging. Specifically, current generation message layers are ill equipped to service the needs of resource-rich clusters, as they are not designed to utilize peripheral devices as globally accessible resources in a cluster.

This thesis focuses on the challenge of designing extensible message layers for this new generation of resource-rich clusters. We are specifically concerned with making peripheral devices available as globally accessible resources in the context of a programming model that permits applications to effectively and efficiently exploit the capabilities afforded by resource-rich clusters.

#### 1.3 Contributions

The key contributions of this thesis fall into two categories. The first includes design concepts and programming abstractions for structuring message layers to integrate powerful peripheral devices into a globally accessible pool of resources. The second class of contributions is engineering solutions to the challenging problems of effectively realizing these design concepts in a manner that tracks the evolution of technology, that is, the continued migration of computing power to distributed resources.

The specific contributions of the thesis are as follows.

- We define a general framework for high-performance, extensible message layers in resource-rich cluster computers. This framework is structured around the following highlevel components.

- A device independent communication core that executes within the network interface and employs i) reliable message delivery mechanisms, ii) a virtual network interface abstraction, iii) an active message programming interface, and iv) a memory transfer programming interface. This communication core is implemented in a message layer for commodity clusters called the General-purpose Reliable In-order Message layer (GRIM).

- O Device dependent functionality is captured in the form of active message function handlers that are implemented within target peripheral devices. Services are provided for the global registration and management of device handlers. Thus, new devices can be integrated and made available for use throughout the cluster in a relatively seamless manner.

- The ability of the core message layer functionality to effectively and efficiently serve as

the host for high-level communication functionality is demonstrated via the

implementation of the following.

- Multicast: A system for replicating multicast messages in the network interface is implemented as an extension to the core communication framework of the message layer. These extensions improve application performance by significantly reducing the workload of communication endpoints during multicast operations.

- Sockets API Emulation: An implementation of a sockets API for the message layer allows legacy applications to leverage system area network hardware for significant improvements in communication performance.

- Streaming Computations Framework: An API and services for pooling peripheral FPGA accelerators across multiple hosts into a unified computing resource allows operations to be performed on high-volume data streams. A unique aspect of this implementation is that device-specific handlers in this case are constructed in hardware, underscoring the generality and flexibility of the GRIM-based services and API.

- The ability of the core message layer functionality to be effectively, efficiently, and

easily integrated with a variety of peripheral devices is illustrated via the integration of

four peripheral devices listed below in increasing degrees of functionality and power.

- AGP Video Display Card: Extensions to the communication library allow distributed endpoints to graphically update remote video display cards in the cluster.

- Brooktree Video Capture Card: The BT8x8 video capture card allows video data streams to be generated and distributed to endpoints in the cluster.

- I<sub>2</sub>O Server Adaptor: This server adaptor card provides intelligent management of both network and storage resources.

- Celoxica RC-1000 FPGA Card: This field-programmable gate array (FPGA) card functions as a computational accelerator through the emulation of applicationspecific circuits in reconfigurable hardware.

This thesis has focused considerable effort on the engineering challenges of harnessing emerging and powerful peripherals and proposing solutions that are comparable with existing message layers in terms of performance. This thesis demonstrates that message layer design, driven by a system-level view and supported by engineering trade-offs that carefully distribute functionality, can provide effective solutions to harnessing the potential of resource-rich clusters.

#### 1.4 Organization of the Thesis

The work presented in this thesis is organized as follows.

- Chapter 2: A brief background of cluster computers is provided to summarize how

clusters have emerged and evolved over the last decade. A fundamental description of

traditional cluster hardware is presented, as well as brief descriptions of existing message

layers for cluster computers.

- Chapter 3: This chapter provides information about the environmental characteristics of resource-rich clusters. Based on these characteristics, fundamental message layer properties for these clusters are discussed.

- Chapter 4: The guidelines for designing a resource-rich cluster message layer are then

applied to implement a real system. This chapter discusses the core functionality of the

GRIM communication library.

- Chapter 5: The performance characteristics of GRIM for traditional transactions between host CPUs is examined and compared with existing work.

- Chapter 6: This chapter provides a description of how commercial peripheral devices can be attached to the GRIM communication library. In order to illustrate the extensible nature of GRIM for supporting hardware, four commercial peripheral devices with different operating characteristics are integrated into the GRIM library. Implementation and performance details are provided for each card.

- Chapter 7: Integrating distributed, specialized computing resources into a unified

infrastructure for an application is the topic of this chapter. Specifically, this chapter

provides insight as to how peripheral devices can be utilized to construct distributed,

computational pipelines.

- Chapter 8: To demonstrate the extensibility of GRIM for application software, this

chapter provides implementation details of a multicast system that performs message

replication in the NI, general-purpose fragmentation and reassembly mechanisms, and an

emulation of a sockets API.

- Chapter 9: The thesis concludes with some summary remarks and directions for future work.

#### **CHAPTER II**

#### BACKGROUND

By the end of the 1980's, the need for high-performance computing platforms in scientific and military applications had resulted in the emergence of a small number of supercomputer companies. These companies constructed large-scale systems that utilized massive amounts of custom hardware to improve application performance. Unfortunately, because these systems were extremely expensive, supercomputers were not a practical option for a large number of end users. Therefore, researchers in the 1990's began exploring alternative high-performance computational platforms that could be constructed in a more cost-effective manner. One of the results of this effort is the field of *cluster computing*. In cluster computing a large number of commercial workstations are collectively utilized to function as a single, multiprocessor system. Since system hardware is comprised of widely available commercial components, cluster computers can be constructed at a fraction of the cost of traditional supercomputers. As such, a considerable amount of high-performance computing research in recent years has focused on improving cluster computer performance.

A key challenge in improving cluster computer performance is adapting commodity hardware and software to function as part of a high-performance, multiprocessor system. Early cluster computing efforts revealed that application performance is highly dependent on the performance of a cluster's communication facilities. From a hardware perspective, several companies have addressed this issue by constructing system area networks (SANs) that provide an order of magnitude improvement over traditional local area networks (LANs). From a software perspective, researchers have constructed specialized communication libraries, or message layers, that are designed to deliver native SAN performance to end applications. In addition to

facilitating low-latency, high-bandwidth communication, these message layers provide a programming abstraction where the cluster is viewed as a pool of host CPUs in a large *virtual* parallel-processing machine. This abstraction has sufficed for numerous researchers to effectively utilize a cluster computer's hardware as a distributed multiprocessor system.

#### 2.1 Evolution of High-Performance Computing Platforms

Supercomputers are the computational systems that deliver the highest peak performance of all computer systems available at a given point in time. These systems typically employ large amounts of custom hardware to accelerate computational performance and often feature specialized computer architectures. Supercomputers have been primarily designed to process complex scientific applications that frequently exhibit large amounts of data parallelism. A number of commercial supercomputer systems have been produced since early groundbreaking work performed by the industry in the 1970's. The evolution of this technology provides both insight into high-performance computing and a motivation to continue the work in related research areas.

#### 2.1.1 A Brief History of Commercial Supercomputers

While numerous people have contributed to the field of supercomputing over the years, perhaps the most influential individual in this effort is pioneer Seymour Cray. After leaving the Control Data Corporation in 1972 to form Cray Research, Cray began work on a new computer architecture that would provide significant gains in peak performance levels. In addition to advances in high-speed circuitry, Cray investigated the use of sophisticated vector processing units that allow computations to be applied to a stream of data to achieve high throughput. In 1976 the Cray-1 [1] was brought to market with a retail value of approximately nine million dollars and a record-breaking performance of 133 million floating-point operations per second (megaflops). In addition to being a technological marvel, the Cray-1 demonstrated that there was

a definite market for expensive high-performance computing systems. Cray continued his work with vector processor systems, producing the 2 gigaflops Cray-2 in 1985 and the 5 gigaflops Cray-3 in 1989. A number of other computers followed the trend of vector processor systems, including the Meiko CS-2 [2], the NEC SX series supercomputer [3], the Fujitsu VP series supercomputer [4], and IBM's vector extensions to the System/370 [5]. Currently, the fastest system in the world [6] is the NEC SX-6, used in the Earth Simulator Center [7] in Japan. This system provides up to 8 teraflops of performance and employs multiple single-chip vector processing units.

The supercomputing industry also explored other architectural techniques for increasing the computational performance of a system. A key effort in this work is the use of a large number of processors to perform computations in parallel. In the SIMD (single instruction stream, multiple data streams) approach, a large number of identical processors perform the same series of operations on different data sets. Multiple SIMD systems were constructed in the early 1990's, including the MasPar Computer Corporation's MP-1 [8] and the Thinking Machines Corporation's CM-2 [9]. Both of these systems housed up to 16,384 SIMD processing elements, and could be used for parallel applications such as image processing. Due to the programming complexity of SIMD, researchers began constructing MIMD (multiple instruction streams, multiple data streams) systems that employed a large number of general-purpose CPUs. This work resulted in massively parallel processing (MPP) systems such as the Intel Paragon [10] (up to 4,000 Intel 80860 processors), the TMC CM-5 [11] (up to 16,000 SUN SPARC processors), and the Cray Research Cray-T3E [12] (up to 2,048 DEC Alpha 21164 processors).

#### 2.1.2 Motivation for Alternate Computing Platforms

While the supercomputer companies of the 1980's provided significant advances in the field of high-performance computing, a large number of these companies withdrew from the supercomputer business in the 1990's. In hindsight it can be said that a common vulnerability for

these companies was the large amount of custom design that was required to build a supercomputer. Several of these companies operated with a vertical design methodology, constructing all components of the system from the individual processors to the interconnection network. While having complete control over the design space gave engineers freedom to innovate performance enhancements, product design times were increased and complicated by the volume of custom hardware design that was required. Therefore, new supercomputers were expensive, brought to market infrequently, and often could not be designed in time to utilize the latest developments in state-of-the-art technology.

Additional issues make traditional supercomputers less appealing to researchers that need high-performance computing platforms. First, supercomputers generally are not scalable and therefore offer a limited lifetime of leading-edge use. An investment in a state-of-the-art supercomputer depreciates rapidly in value due to Moore's Law, thereby making current systems obsolete within 18 months. Second, supercomputers require specialized hardware and software maintenance that adds to the expense of ownership. These components can be expensive to replace and there are generally few people that are trained to perform such maintenance. Finally, it must be noted that a risk in purchasing a traditional supercomputer is that the manufacturer might go out of business or otherwise abandon support for a particular product. Maintaining and utilizing orphaned hardware is time consuming and ultimately impedes end users.

Given the problems associated with using traditional supercomputers, a number of researchers in the early 1990's began exploring alternative methods by which high-performance computational platforms could be constructed. This effort made several observations about commercial technological advances and the global marketplace that would influence the construction of future parallel-processing systems. These observations include the following:

Commercial Off-the-Shelf (COTS) Parts: In industry there are numerous corporations

producing state-of-the-art hardware and software components. By using COTS parts,

designers leverage other people's work and reduce the design time for a system. COTS parts are also beneficial because components can easily be replaced or upgraded from third-party products.

- Growth in the Workstation and Network Markets: Consumer demand for personal computers has resulted in high-performance workstations that are available at a low cost. Processor design in this market remains competitive, resulting in frequent updates to peak performance levels. Likewise, consumer interest in the Internet has resulted in advances in network hardware. The need for faster networks has resulted in low-cost local area networks (LANs) that economically offer high-bandwidth communication.

- A Rich Software Environment: An important aspect of commodity workstations is the

wide availability of software. Operating systems such as GNU/Linux provide a UNIXlike environment with built-in network features. The open source nature of Linux allows,

researchers to easily incorporate custom functionality into the operating system kernel.

In summary, researchers observed that advances made in consumer markets in the 1980's and 1990's had resulted in hardware that was widely available, economical, and offered respectable levels of computational performance. These systems could be utilized to provide impressive price-to-performance ratios and have benefited from considerable efforts to improve the PC's software environment.

#### 2.1.3 Emergence of Cluster Computers