### **SANDIA REPORT**

SAND2006-6888 Unlimited Release Printed November 2006

# FPGAs in High Performance Computing: Results from Two LDRD Projects

K. Scott Hemmert, Keith D. Underwood, Craig D. Ulmer, David C. Thompson

Prepared by Sandia National Laboratories Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the United States Department of Energy's National Nuclear Security Administration under Contract DE-AC04-94-AL85000.

Approved for public release; further dissemination unlimited.

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from U.S. Department of Energy Office of Scientific and Technical Information

> P.O. Box 62 Oak Ridge, TN 37831

Telephone: (865) 576-8401 Facsimile: (865) 576-5728

E-Mail: reports@adonis.osti.gov

Online ordering: http://www.osti.gov/bridge

Available to the public from

U.S. Department of Commerce National Technical Information Service 5285 Port Royal Rd Springfield, VA 22161

Telephone: (800) 553-6847 Facsimile: (703) 605-6900

E-Mail: orders@ntis.fedworld.gov

Online ordering: http://www.ntis.gov/help/ordermethods.asp?loc=7-4-0#online

### SAND2006-6888 Unlimited Release Printed November 2006

# FPGAs in High Performance Computing: Results from Two LDRD Projects

K. Scott Hemmert

Keith D. Underwood

Scalable Computing Systems Department

Sandia National Laboratories

P.O. Box 5800

Albuquerque, NM 87185-1319

kshemme@sandia.gov

kdunder@sandia.gov

Craig D. Ulmer

David C. Thompson

Visualization and Scientific Computing Department

Sandia National Laboratories

P.O. Box 969

Livermore, CA 94551-0969

cdulmer@sandia.gov

dcthomp@sandia.gov

#### **Abstract**

Field programmable gate arrays (FPGAs) have been used as alternative computational devices for over a decade; however, they have not been used for traditional scientific computing due to their perceived lack of floating-point performance. In recent years, there has been a surge of interest in alternatives to traditional microprocessors for high performance computing. Sandia National Labs began two projects to determine whether FPGAs would be a suitable alternative to microprocessors for high performance scientific computing and, if so, how they should be integrated into the system. We present results that indicate that FPGAs could have a significant impact on future systems. FPGAs have the *potential* to have order of magnitude levels of performance wins on several key algorithms; however, there are serious questions as to whether the system integration challenge can be met. Furthermore, there remain challenges in FPGA programming and system level reliability when using FPGA devices.

# Acknowledgment

Arun Rodrigues provided valuable support and assistance in the use of the Structural Simulation Toolkit within an FPGA context. Curtis Janssen and Steve Plimpton provided valuable insights into the workings of two Sandia applications (MPQC and LAMMPS, respectively).

## **Contents**

| Pr | reface                                                  | 14 |

|----|---------------------------------------------------------|----|

| Su | ımmary                                                  | 15 |

| No | omenclature                                             | 16 |

| 1  | Introduction                                            | 17 |

| 2  | Related Work                                            | 21 |

|    | Floating-Point Algorithms                               | 21 |

| 3  | High Performance Floating-Point Modules                 | 23 |

|    | General Implications for Floating-Point Implementations | 23 |

|    | Floating-Point Unit Implementation                      | 24 |

|    | General Considerations                                  | 24 |

|    | Adder Implementation                                    | 25 |

|    | Multiplier Implementation                               | 27 |

|    | Characteristics                                         | 29 |

| 4  | Implications of Trends in FPGA Performance              | 31 |

|    | Trends in FPGA Performance                              | 31 |

|    | Addition                                                | 32 |

|    | Multiplication                                          | 33 |

|    | Division                                                | 33 |

|    | Multiply Accumulate                                     | 35 |

|   | Analysis                               | 33 |

|---|----------------------------------------|----|

|   | Analysis Retrospective                 | 37 |

|   | Kernels Explored in Simulation         | 38 |

|   | Matrix Multiply                        | 38 |

|   | FPGA Implementation                    | 40 |

|   | Performance Comparisons                | 41 |

|   | Memory Requirements                    | 42 |

|   | Matrix-Vector Multiply                 | 43 |

|   | FPGA Implementation                    | 43 |

|   | Performance Comparisons                | 46 |

|   | Fast Fourier Transform (FFT)           | 47 |

|   | Parallel FFT Implementation            | 49 |

|   | Pipelined FFT Implementation           | 50 |

|   | Parallel-Pipelined FFT Implementation  | 52 |

|   | Comparison of Architectures            | 53 |

|   | FPGAs vs. CPUs                         | 54 |

|   | Analysis Summary                       | 56 |

| 5 | Implementations on a Real World System | 57 |

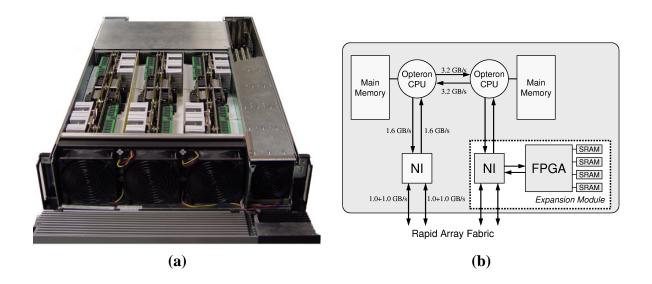

|   | The Cray XD1                           | 57 |

|   | Development Components                 | 58 |

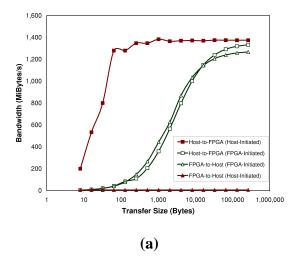

|   | CPU-FPGA Data Transfers in the XD1     | 59 |

|   | Application Examples                   | 60 |

|   | k-Nearest Neighbors (kNN)              | 62 |

|   | Stiffness Matrix (STIFF)               | 66 |

|   | Ray-Triangle Intersection (RTI)        | 70 |

| Re | eferences                     | 100 |

|----|-------------------------------|-----|

| 8  | Conclusions                   | 99  |

|    | Reliability                   | 97  |

|    | Cost                          | 96  |

|    | Architecture                  | 96  |

|    | Portability                   | 96  |

|    | Programmability               | 95  |

|    | Algorithms                    | 95  |

| 7  | Challenges to Deploying FPGAs | 95  |

|    | Summary                       | 93  |

|    | Simulation Results            | 90  |

|    | Measurements from the XD1     | 88  |

|    | Approach                      | 86  |

|    | Benchmarks                    | 86  |

|    | Structural Simulation Toolkit | 86  |

|    | Pentium-4 Xeon Workstation    | 85  |

|    | Cray XD1                      | 84  |

|    | Methodology                   | 84  |

|    | Motivating Applications       | 83  |

|    | Motivation and Methodology    | 83  |

| 6  | System Simulation             | 83  |

|    | XD1 Observations              | 80  |

|    | Application Summary           | 79  |

|    | Isosurfacing (ISO)            | 75  |

# **List of Figures**

| 1.1  | A high-level representation of an FPGA                                                                                    | 18 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | IEEE double precision floating-point format                                                                               | 23 |

| 3.2  | General computation layout for the floating-point adder                                                                   | 26 |

| 3.3  | General computation layout for the floating-point multiplier                                                              | 28 |

| 4.1  | Double precision floating-point performance                                                                               | 34 |

| 4.2  | Floating-point double precision multiply accumulate performance                                                           | 35 |

| 4.3  | Basic FPGA property trends                                                                                                | 36 |

| 4.4  | Maximum achievable performance versus memory bandwidth and matrix size                                                    | 39 |

| 4.5  | Matrix multiply implementation                                                                                            | 40 |

| 4.6  | A comparison of double precision floating-point matrix multiplication performance on CPUs, FPGAs, and RC platforms        | 41 |

| 4.7  | Matrix multiply internal memory analysis                                                                                  | 43 |

| 4.8  | Maximum sustainable matrix vector multiply performance versus memory bandwidth                                            | 44 |

| 4.9  | Multiply-accumulate unit                                                                                                  | 45 |

| 4.10 | Matrix vector multiplication implementation                                                                               | 45 |

| 4.11 | A comparison of double precision floating-point matrix-vector multiplication performance on CPUs, FPGAs, and RC platforms | 46 |

| 4.12 | Basic butterfly operation and hardware implementation                                                                     | 48 |

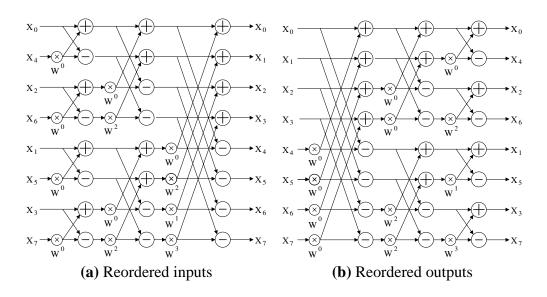

| 4.13 | Two variations of 8-point, radix-2 FFTs                                                                                   | 48 |

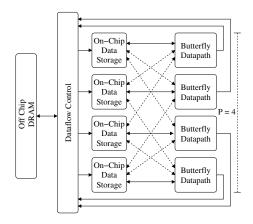

| 4.14 | Architecture of the Parallel FFT                                                                                          | 50 |

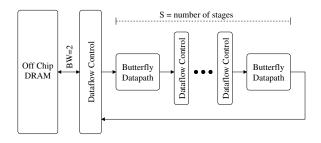

| 4.15 | Architecture of the Pipelined FFT                                                                                         | 51 |

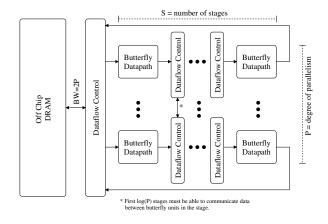

| 4.16 | Architecture of the Parallel-Pipelined FFT                                                                                      | 52 |

|------|---------------------------------------------------------------------------------------------------------------------------------|----|

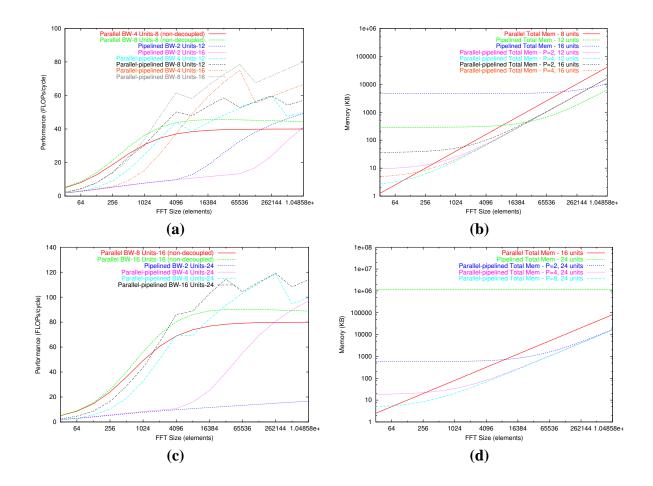

| 4.17 | A comparison of the performance and memory requirements of FFT implementations                                                  | 53 |

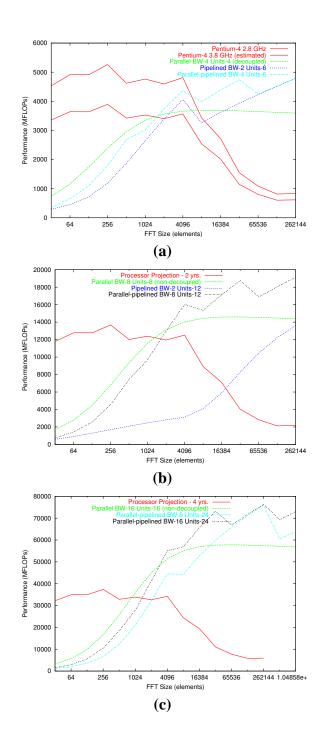

| 4.18 | FPGAs vs. CPUs for FFT on current and projected technologies                                                                    | 55 |

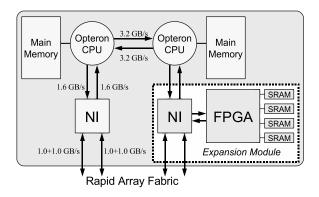

| 5.1  | The Cray XD1 Architecture                                                                                                       | 58 |

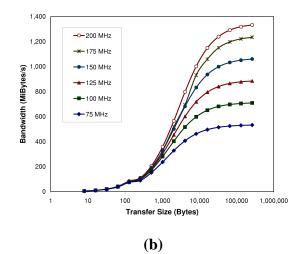

| 5.2  | Data transfer characteristics of the XD1                                                                                        | 60 |

| 5.3  | The pseudo-code for the kNN algorithm                                                                                           | 62 |

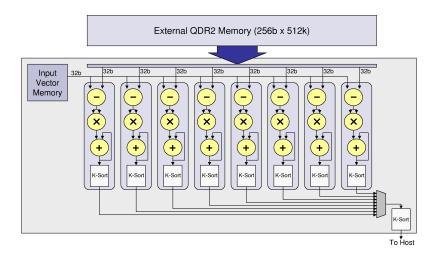

| 5.4  | Architecture of the kNN Hardware Accelerator                                                                                    | 64 |

| 5.5  | The pseudo-code for the modified kNN algorithm                                                                                  | 64 |

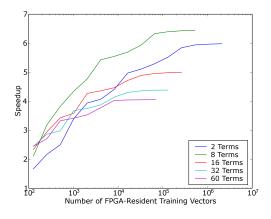

| 5.6  | Performance gain of FPGA accelerator for kNN                                                                                    | 65 |

| 5.7  | Pseudo-code for the stiffness matrix computation at a single mesh point. Matrix indices are omitted in this listing for brevity | 67 |

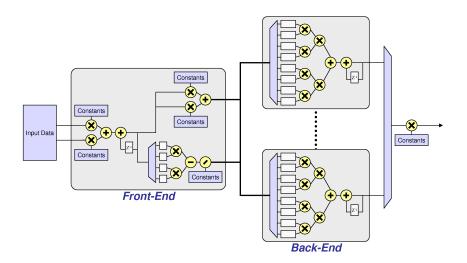

| 5.8  | Architecture of the STIFF Hardware Accelerator                                                                                  | 69 |

| 5.9  | Pseudo-code for the Möller-Trumbore Ray-Triangle Intersection (RTI) Algorithm                                                   | 70 |

| 5.10 | Pseudo-code for RTI Work in a Photon Mapping Application                                                                        | 71 |

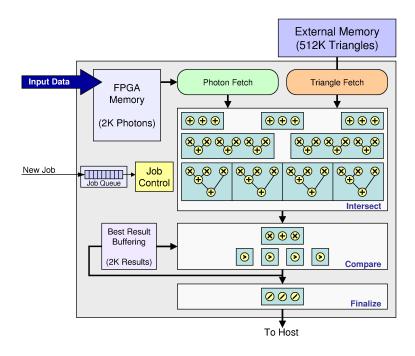

| 5.11 | Architecture of the Ray-Triangle Intersection hardware accelerator                                                              | 73 |

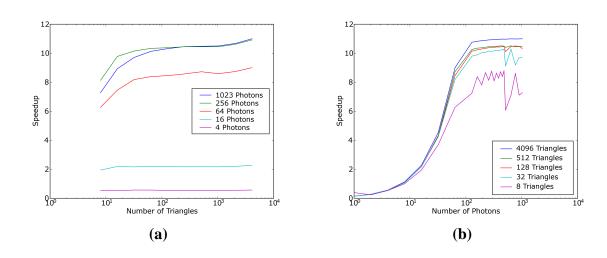

| 5.12 | Speedup of the RTI Hardware Accelerator over Software                                                                           | 74 |

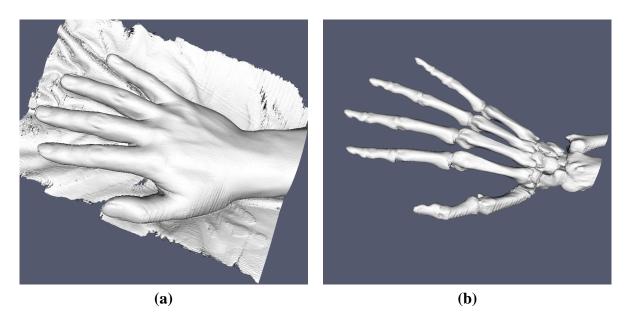

| 5.13 | Exterior and interior views of a hand by isosurfacing                                                                           | 75 |

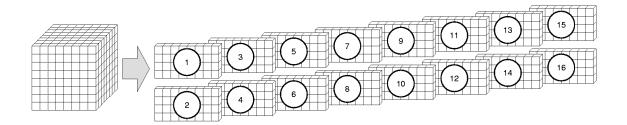

| 5.14 | Rather than processing an entire cube at a time, the isosurfacing accelerator processes slices of data                          | 77 |

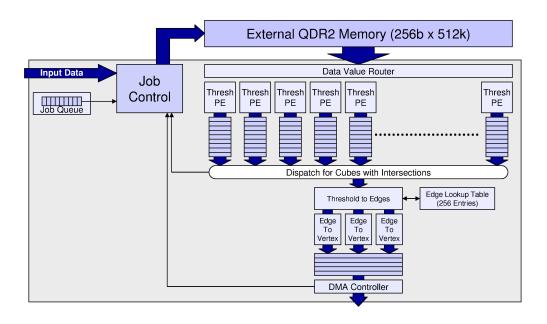

| 5.15 | Architecture of the isosurfacing accelerator                                                                                    | 78 |

| 6.1  | The XD1 architecture                                                                                                            | 85 |

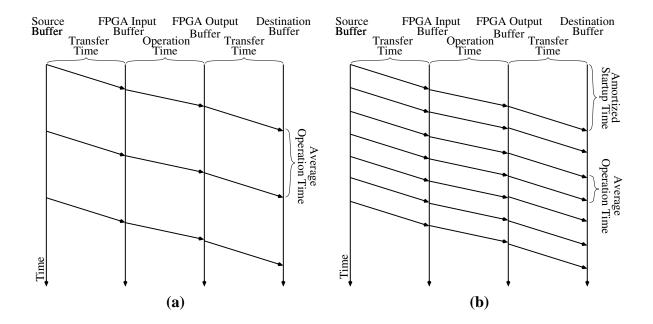

| 6.2  | The traditional (a) and modified (b) benchmarks                                                                                 | 86 |

| 6.3  | Blocking vs. Non-blocking approaches                                                                                            | 87 |

| 6.4  | Timeline for blocking and non-blocking operations                                                                               | 87 |

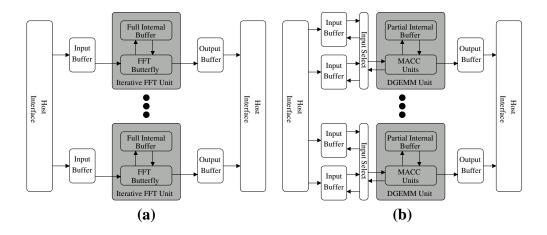

| 6.5  | Ruffer approaches for FET and DGEMM                                                                                             | 88 |

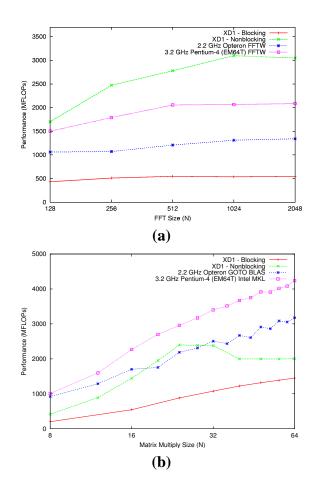

| 6.6 | XD1 performance comparison for FFT and DGEMM                  | 89 |

|-----|---------------------------------------------------------------|----|

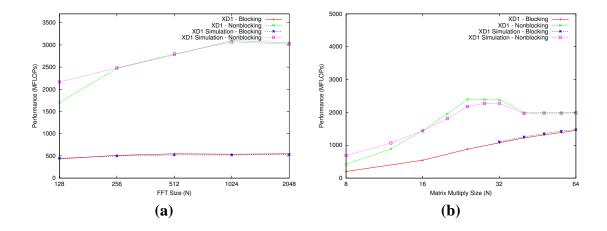

| 6.7 | Validation of the simulation models for (a) FFT and (b) DGEMM | 90 |

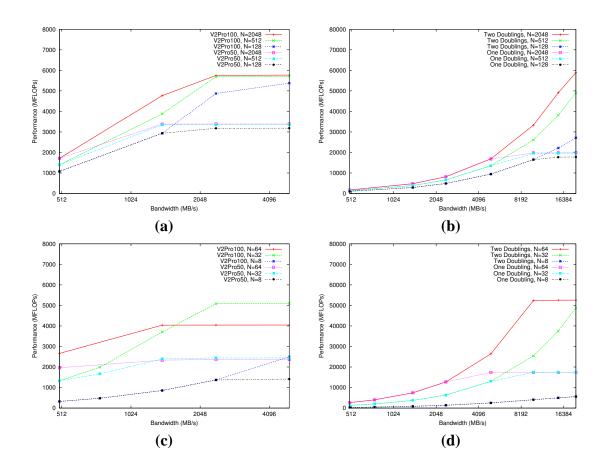

| 6.8 | Simulated impact of bandwidths for FFT and DGEMM              | 92 |

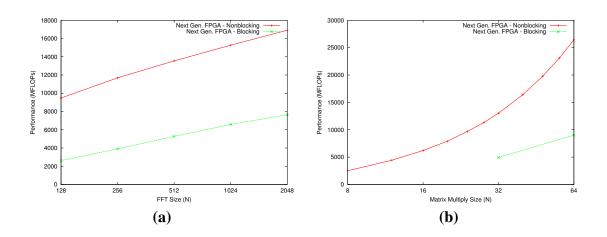

| 6.9 | Simulated impact of blocking operations for FFT and DGEMM     | 92 |

## **List of Tables**

| 3.1 | Special values in the IEEE 754 format                                                                     | 24 |

|-----|-----------------------------------------------------------------------------------------------------------|----|

| 3.2 | Original Floating-point Units versus Optimized Units (size in slices, latency in cycles and speed in MHz) | 25 |

| 3.3 | Floating-point Unit Characteristics (size in slices, latency in cycles and speed in MHz)                  | 30 |

| 4.1 | Parts used for performance comparison                                                                     | 32 |

| 4.2 | Parallel pipeline shapes                                                                                  | 54 |

| 4.3 | Memory requirements summary                                                                               | 54 |

| 5.1 | Characteristics of the four XD1 accelerator designs                                                       | 79 |

| 6.1 | Typical system parameters                                                                                 | 84 |

## **Preface**

As requested by the IAT, this final report combines the results and experiences from two LDRD projects exploring the potentials of FPGAs for impacting high performance computing. The two projects (High Performance Processing architecture (67016) and Enhancing Simulation Performance on Clusters with Configurable Auxiliary Devices (67018)) began as independent efforts, but converged in their final year. The different approaches may be apparent throughout the document, but we have attempted to merge the results to present a cohesive conclusion.

## **Summary**

Field-programmable gate arrays (FPGAs) are a technology that has received a lot of attention in the high performance computing (HPC) community over the last few years. While FPGAs are widely accepted to offer a tremendous value in metrics such as performance and performance/power for a significant class of applications, they have not traditionally been used for the scientific computing applications common on most HPC platforms. In early literature, results indicated that FPGAs were a poor match to floating-point arithmetic — and this view was still prevalent in the fall of 2003 when Sandia National Labs started two projects to explore the use of FPGAs in HPC environments.

In New Mexico, the "High Performance Processing Architecture" project began exploring the capabilities of FPGAs to support double precision floating-point arithmetic. Our goal was to determine what levels of peak performance could be achieved on an FPGA and to determine how common scientific applications would map to FPGAs. We also had a stated objective of determining how the FPGAs could be integrated into the system.

In California, the "Enhancing Simulation Performance on Clusters with Configurable Auxiliary Devices" project focused on communication challenges associated with integrating accelerators into modern HPC systems. This effort focused on both network-based approaches (i.e., connecting an FPGA to the system's network fabric) and localized approaches (i.e., connecting an accelerator to the host's I/O subsystem). Multiple applications were adapted to utilize the FPGA resources in order to gain a better understanding of what can be achieved with current generation technology.

Our results indicate that FPGAs *could* have a dramatic advantage (10× within the decade) in peak floating-point performance — if the FPGA vendors decide to focus on the HPC market. These advantages translate into an even greater advantage in sustained performance because the FPGA system can be engineered to deliver dramatically more memory bandwidth than conventional processors will ever deliver.

Unfortunately, there remain a number of challenges to deploying FPGAs that have not yet been solved. FPGAs are still remarkably difficult to program and are unlikely to execute fully general purpose code in the near future. Thus, FPGAs must be integrated into a system along with a conventional microprocessor. Our results suggest that this system integration is a particular challenge as FPGAs of the future will need a tight coupling with the processor through a high bandwidth interface. Indeed, the bandwidth requirements could become so great as to become unachievable. Finally, major reliability issues remain with single-event upsets (SEU) that preclude a large scale deployment of FPGAs in the near term.

## **Nomenclature**

**8B/10B** A standard encoding scheme used to protect data in communication networks

**BRAM** Block Ram. A dual-ported bank of memory available within the Xilinx FPGA architecture

**CRC** Cyclic Redundancy check: a hash function used to detect errors in data transmissions

**CT** Computed Tomography

**DSP48** A specialized block in Xilinx Virtex4 FPGAs designed to enhance DSP performance. The DSP48 is essentially a multiply-accumulate block with additional logic to cascade multiple blocks together to create larger operations. A single block can do a 18x18 bit signed multiply followed by a 48-bit addition.

**FFT** Fast Fourier Transform

**FPGA** A field-programmable gate array is a hardware device that can be reprogrammed at the hardware level on a per application basis. FPGAs are programmed at a particularly fine grain (gates and flip-flops).

**HDL** Most FPGA designs are done using a hardware description language (HDL); however, many efforts are now considering high level language (HLL) compilers.

**MGT** Multi-Gigabit Transceiver (e.g., Rocket I/O)

MRI magnetic resonance imaging

**PE** processing element — a single computational block for a particular function

**Reconfigurable Computing** Reconfigurable computing refers to the practice of using programmable hardware — hardware that can be "reconfigured" — to implement computing algorithms.

Rocket I/O Multi-Gigabit transceivers in the Xilinx FPGA

**RTI** Ray-Triangle Intersection

**SERDES** Serialization/Deserialization — Process of converting between serial and parallel data representations

**TCP** Transmission Control Protocol - a widely used standard for reliably transmitting data over a network

## Chapter 1

## Introduction

The field of reconfigurable computing dates back almost 15 years. It focuses on the use of *programmable hardware* to implement computational algorithms. In contrast with traditional microprocessors, programmable hardware tends to run at lower clock rate, but exposes several orders of magnitude more parallelism. In contrast with ASICs (application specific integrated circuits), programmable hardware is significantly slower, but dramatically more flexible. Whereas ASICs are typically designed for exactly one purpose, programmable hardware can be reprogrammed (reconfigured) to meet the needs of whatever application is running. Thus, reconfigurable computing is often billed as delivering ASIC levels of performance with microprocessor levels of flexibility. In practice, reconfigurable computing typically uses field-programmable gate arrays (FPGAs) as the programmable hardware fabric.

FPGAs are reconfigurable hardware devices that can be programmed to emulate custom digital hardware that is specified by the end user. FPGA vendors such as Xilinx and Altera offer a variety of FPGA products that vary in terms of gate capacity (thousands to millions of user logic gates), power consumption (milliwatt to 20 watts), and cost (\$20 to \$5,000). While FPGAs are primarily utilized for prototyping designs before they are fabricated as ASICs, recent cost and size improvements have motivated industry to utilize FPGAs as ASIC replacements. These improvements have driven a renewed interest in utilizing FPGAs for reconfigurable computing research, as the larger and faster the FPGA, the more work that can be performed in a single chip.

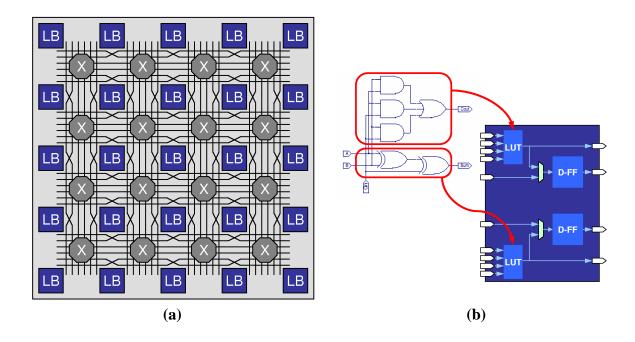

One of the reasons why FPGA vendors are capable of rapidly improving their products is that FPGAs are tiled architectures. As illustrated at a high level in Figure 1.1, FPGAs utilize a two-dimensional array of programmable logic blocks (LBs) to implement the functionality of a user's design. An individual LB is comprised of one or more n-input lookup tables (LUTs), simple routing logic, and one or more memory elements. At design compile time, hardware synthesis tools map the logic functions in a design to truth tables that can be programmed into LUTs. The tools then place the LUTs in specific LBs and generate static routes through the FPGA to interconnect resources in the FPGA as required by the design.

In order to expand into new markets, FPGA vendors have recently begun to include special-purpose hardware units in their FPGA architectures. The "platform FPGAs" provide devel-

**Figure 1.1.** (a) A high-level representation of an FPGA. (b) The mapping of a logic function to the LUTs of a LB.

opers with internal memory banks, integer arithmetic units, high-speed network transceivers, and even dedicated embedded microprocessors. For example, the largest FPGA in the Xilinx Virtex-II/Pro family features a megabyte of internal memory, twenty 3 Gb/s network transceivers, and two 400 MHz PowerPC 405 processors. These resources make current generation FPGAs more suitable for different kinds of applications and encourage researchers to utilize FPGAs in ways that were previously infeasible.

FPGAs have been demonstrated as great performers on DSP algorithms. They show order of magnitude (or more) benefits in every category from performance to performance/cost to performance/power. Indeed, FPGAs are beginning to dominate markets that were once controlled by ASICs and markets that were controlled by DSP processors. For example, many satellite programs use FPGAs. One big contrast between the DSP domain and the high performance computing (HPC) domain is the precision of the arithmetic. Where DSP and image processing applications typical use low precision numbers (narrow integers, fixed point, narrow floating-point), scientific applications using traditional HPC resources typically require double precision floating-point. In the past, research has indicated that FP-GAs were inappropriate for such operations, but the work that spawned these two projects suggests that the latest FPGA devices can perform respectable amounts of floating-point arithmetic. Furthermore, a plethora of companies now offer FPGA based accelerators for HPC systems. Thus, two LDRD projects were created to explore whether FPGAs could be applied to traditional HPC and, if so, how.

Our research has demonstrated that FPGAs work quite well for double precision floatingpoint. In fact, some trends suggest that FPGAs could actually provide a significantly higher amount of peak floating-point performance than microprocessors in the near future. More remarkably, the investigation of algorithms on FPGAs has suggested that FPGAs could sustain a much higher percentage of that peak performance than microprocessors. In many cases, this is driven by market forces. Microprocessor vendors must deliver parts to a broad commercial market that does not have the level of bandwidth demands that many scientific applications have. Thus, for reasons of cost-effectiveness, microprocessors provide a relatively small amount of memory bandwidth. FPGAs, in contrast, target a market that needs abundant configurable I/O pins on the device. These I/O pins can be targeted to any purpose; thus, for the HPC market, we could choose to build a system where the FPGA used all of those pins for memory and had abundant memory bandwidth. In addition, although not shown here, other research has indicated that Sandia's scientific applications have more integer computations than floating-point computations. Microprocessors are balanced for equal amounts of integer and floating-point arithmetic, but FPGAs can dedicate resources in whatever balance is required. More importantly, integer computations are the thing that FPGAs do best; thus, this could give FPGAs a significant advantage.

As a means of complementing our investigation into floating-point use in FPGAs, we also investigated how much acceleration could be obtained in a practical sense from a real-world system. For this work we obtained a Cray XD1 system, which features an architecture that provides a tight coupling between host CPUs and FPGA accelerators. After examining the low-level characteristics of the XD1 and developing missing infrastructure, we adapted multiple computational kernels to the XD1's FPGAs and compared the performance difference between software and hardware implementations. These experiments revealed several observations. First, we were able to achieve speedups in all four of our examples even though our XD1 is only equipped with mid-sized FPGAs. While increasing the FPGA's capacity makes it easier to exploit parallelism, it is promising to know that clever architectural planning can still yield performance wins. Second, in multiple cases we found that the FPGA could easily out-pace the data rate of its connection to host memory. Thus, as good as an FPGA design may be, performance can ultimately be limited by the performance characteristics of the host in which it resides. Finally, adapting an algorithm to hardware (and getting it all to produce the right answers) is a time consuming process. Our application kernels and the corresponding host software took between three weeks and three months to develop and debug.

Having found a number of algorithms where FPGAs perform well, we also explored questions of system integration. This work had two facets: a practical implementation of network integration components and a simulation based study of an FPGA coupled directly to a microprocessor. In the network integration work we focused on the task of incorporating FPGA resources into an existing HPC system by connecting the FPGAs to the system's communication network. In order to achieve this goal, we investigated the communication capabilities of the Xilinx Virtex-II/Pro's Rocket I/O modules. We ultimately implemented a fully-functional network interface (NI) that is comprised of a TCP/IP Offload Engine (TOE) and a Gigabit Ethernet (GigE) unit. We found that the network-based approach

to system integration was particularly useful in visualization applications (e.g., when an FPGA is used to generate data that is rendered by a cluster-driven, tiled display wall). The strength of this approach is that by relying on the network to bridge the gap between systems, FPGAs could be utilized in a flexible manner. However, it would be ill-advised for us to suggest that this approach is the right one for general HPC applications. The primary downside is that networks place a great deal of communication distance between CPUs and FPGAs. While some applications can tolerate this latency, it is a significant hindrance to application developers. In studying the interaction with a local microprocessor, we found that a broad class of operations had very little dependency on the latency of the connection, but a strong dependence on the bandwidth. In fact, the bandwidth requirements of future parts could reach so high as to make the coupling impractical. Perhaps more surprisingly, we found that the proposal by many to simply intercept existing library calls for operations such as matrix multiply or Fast Fourier Transform (FFT) would simply not work for the types of application usage scenarios at Sandia. Instead, a much better (non-blocking) interface would be required.

Despite many positive results, many challenges remain. While our studies have highlighted some important architectural characteristics, it will still be necessary to define a good architecture for integrating the FPGAs into a system. A good architecture will then need better ways to program the FPGA — application developers will not want to devote months learning to program hardware and weeks coding even the most simple of operation. In the current state of the art, the resulting programs would be locked to a single platform and it is unlikely that application developers would be willing to tolerate that lack of portability. Furthermore, current FPGA systems face distinct reliability challenges that must be addressed before they can be integrated into traditional HPC systems. Finally, the current cost of FPGA systems currently overshadows their impressive performance. The HPC market will need at least an order of magnitude improvement in a performance/cost metric over traditional systems to make it worth their effort.

## Chapter 2

### **Related Work**

This work is motivated by an extensive body of previous work in floating-point for FPGAs. A long series of work[33, 2, 5, 10, 22] has investigated the use of custom floating-point formats in FPGAs. There has also been some work in the translation of floating-point to fixed point[21] and the automatic optimization of the bit widths of floating-point formats[11]. In most cases, these formats are shown to be adequate for some applications, to require significantly less area to implement than IEEE formats[17], and to run significantly faster than IEEE formats. Most of these efforts demonstrate that such customized formats enable significant speedups for certain chosen applications. Unfortunately, many scientific applications depend on both the dynamic range and high precision of IEEE double-precision floating-point to maintain numerical stability. Thus, this work focuses on the IEEE standard. Indeed, some application developers within the DOE labs are beginning to discuss the need for greater precision than the standard IEEE formats, and such formats may be the topic of future work.

The earliest work on IEEE floating-point[7] focused on single precision and found that, although feasible, it was extremely slow. Later work[25] found that the performance was improving, but still relatively poor. Eventually, it was demonstrated[23] that while FPGAs were uncompetitive with CPUs in terms of peak FLOPs, they could provide competitive sustained floating-point performance. Since then, a variety of work[26, 2, 22, 40] has demonstrated the growing feasibility of IEEE compliant, single precision floating-point arithmetic and other floating-point formats of approximately that complexity. Indeed, some work[34] suggests that a collection of FPGAs can provide dramatically higher performance than a commodity processor.

### **Floating-Point Algorithms**

Our earliest work[37, 38] demonstrated that FPGAs can indeed provide competitive floating-point performance with a potential for an order of magnitude win in the relatively near future This sparked a wave of research into the intersection of traditional high performance, scientific computing and FPGA based reconfigurable computing that paralleled our own work. Studies have indicated that FPGA can deliver high performance with the levels of precision needed by scientific computing[15, 13, 14, 12, 45, 46, 44, 6, 4, 47]. Numerous

efforts have also begun to study double precision floating-point from the relatively simple matrix multiply[44] operations to the more complex LU decomposition[12] and sparse matrix-vector operations[47, 4].

The weakness in the majority of these studies, however, is that they do not consider either the API to deliver the performance to the application or the system architecture issues such as bandwidth and latency to the accelerator. Of these recent works, only a handful have discussed how the performance could be incorporated into an application. The three most notable examples are a molecular dynamics application[20, 32], a full CG solver[28], and a traffic simulation engine[36]. The major contribution of Sandia has been to consider the system level implications of such systems and the requirements for future systems.

## Chapter 3

# **High Performance Floating-Point Modules**

### **General Implications for Floating-Point Implementations**

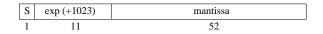

Floating-point arithmetic is fundamentally different from typical integer or fixed-point arithmetic. Where integer and fixed-point values are typically stored in two's complement, floating-point numbers are typically stored in signed-magnitude format. Floating-point numbers also add an exponent field to control the position of the decimal point in the value. The most widely used floating-point format is the IEEE 754 standard. As an example, the IEEE double precision floating-point format is shown in Figure 3.1. The mantissa (fraction part) is 52 bits, the exponent is 11 bits, and the sign is a single bit.

As the figure suggests, the exponent in the IEEE format is maintained in *biased* notation. For double precision, the bias is 1023 (approximately half the range), meaning an exponent of -1022 is stored as a 1. The second complication in the format is the use of an implied 1. An implied 1 means that the stored number is maintained in a normalized format such that there is a 1 immediately to the left of the decimal and the decimal is immediately to the left of the stored value. This allows the format to have an extra bit of precision without having to store it. Thus, the value can be extracted as shown in Equation 3.1.

$$(-1)^S \times 2^{exp-bias} \times 1.mantissa$$

(3.1)

There are also several special values define in the IEEE standard. These values are formed by using the reserved exponent values of all ones and all zeroes. The special values are zero,  $\pm \infty$ , and Not a Number (NaN), which is used as the result of meaningless operations (e.g.  $\infty \times 0$ ). The reserved special values are summarized in Table 3.1. There is also a class

**Figure 3.1.** IEEE double precision floating-point format

**Table 3.1.** Special values in the IEEE 754 format

| Special Value | Sign | Exponent | Mantissa |  |  |

|---------------|------|----------|----------|--|--|

| Zero          | 0/1  | 0        | 0        |  |  |

| ∞             | 0    | MAX      | 0        |  |  |

| -∞            | 1    | MAX      | 0        |  |  |

| NaN           | 0/1  | MAX      | non-zero |  |  |

| Denormal      | 0/1  | 0        | non-zero |  |  |

of values known as denormals, which are represented by a zero exponent and non-zero mantissa.

Denormals are a special form of IEEE floating-point numbers that provide a small amount of extra precision as the result of an operation approaches underflow. Unlike most IEEE floating-point numbers, they do not include the implied one. Instead, they have an exponent of zero, keep the decimal immediately to the left of the stored value, and allow the first one to fall anywhere in the stored value. Floating-point hardware within a microprocessor typically implements denormals with an exception that then computes the value via software. However, in an FPGA-based implementation, to support full IEEE floating point we must generally add denormal support into the hardware itself. Thus, for denormal numbers, the value is extracted as in Equation 3.2.

$$(-1)^S \times 2^{1-bias} \times 0.mantissa \tag{3.2}$$

### **Floating-Point Unit Implementation**

The library developed as part of this project includes modules for addition, multiplication, division and square root. Of these units, the most important are the adder and multiplier, as they are the most commonly used. In light of this, these units have had correspondingly more effort put into optimizing them and are discussed in more detail here.

#### **General Considerations**

The optimized floating-point units were adapted from units created for another research project. The original units were written in VHDL and formed the basis of the optimized units discussed here. There were two reasons to optimize these units: First, modern FP-GAs are only now reaching a competitive state with CPUs in terms of floating-point performance, so the base floating-point units need to provide as much performance as possible. Second, the FPGA tools had a difficult time maintaining high clock frequencies when many units were used in a large design. In order to improve both of these, it was decided that

**Table 3.2.** Original Floating-point Units versus Optimized Units (size in slices, latency in cycles and speed in MHz)

| Virtex2Pro (-6 speed grade) |       |     |            |      |     |       |

|-----------------------------|-------|-----|------------|------|-----|-------|

| Precision                   | Adder |     | Multiplier |      | ier |       |

|                             | Size  | Lat | Speed      | Size | Lat | Speed |

| Single                      | 495   | 13  | 195        | 592  | 16  | 176   |

| Single - Optimized          | 328   | 10  | 268        | 345  | 11  | 267   |

| Double                      | 1090  | 14  | 143        | 1608 | 20  | 142   |

| Double - Optimized          | 571   | 10  | 204        | 905  | 12  | 207   |

the units needed to be hand-mapped<sup>1</sup> and relationally placed to provide the best possible performance. The optimized units are written in JHDL[16], which is a structural design language that allows easy mapping and placing of logic.

The process of hand-mapping the units lead to further architectural enhancements. The enhancements allowed for further reductions in size and latency and an increase in operating frequency. In addition, the relational placement allows the units to maintain higher clock frequencies in large designs. Table 3.2 shows the size, speed and latency of the original and optimized adder and multiplier for both double and single precision. The values are taken for the Virtex2Pro (-6 speed grade), which was one of the fastest parts available at the time the original library was written.

The table shows that the optimizations provided a 1.8-1.9x improvement in area and a 1.4x increase in clock frequency for the double precision modules. This provided a total performance improvement of 2.7x for the adder and 2.6x for the multiplier.

### Adder Implementation

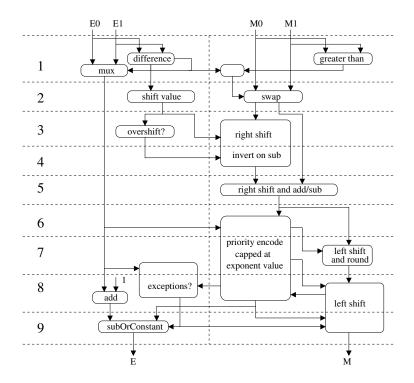

The double precision adder consists of 9 operational stages. The general makeup of these stages can be seen in Figure 3.2. The fully pipelined version of the adder registers the data between each stage (indicated by dashed lines in the figure), and additionally registers the input before any computation is done, resulting in a latency of 10 clock cycles. The stages were designed to utilize all inputs to the 4-LUTs whenever possible. This results in both smaller, faster, and lower latency units.

The first two stages inspect the inputs and prepare them for the alignment step. This includes determining if either of the inputs is one of the IEEE special values, computing the alignment shift and swapping the smaller number into the alignment path. The larger exponent is also chosen as the interim exponent.

<sup>&</sup>lt;sup>1</sup>Logic mapping consists of determining how the logic of the circuit maps to the FPGA structure, which consists mainly of 4-LUTs, but also has other auxillary logic that must be taken into account.

**Figure 3.2.** General computation layout for the floating-point adder

The third through fifth stages align the mantissas and perform the actual operation. Alignment is done through a series of shifting, conceptually implemented by stages which shift by different powers of 2, allowing any shift value from 0 to 53 to be generated. The majority of the shifting happens in stages 3 and 4, but the final shift by 1 is merged with the addition logic. Stages 6 through 9 are used to round the mantissa and renormalize it, if necessary. Again, in order to reduce circuit size, one stage of shifting is merged with the aritmetic logic which does the rounding. This happens in stage 7, while the rest of the shifting occurs in the final two stages. In addition to work on the mantissa, stages 7 through 9 also clean up the exponent and handle a variety of exception conditions.

### **Multiplier Implementation**

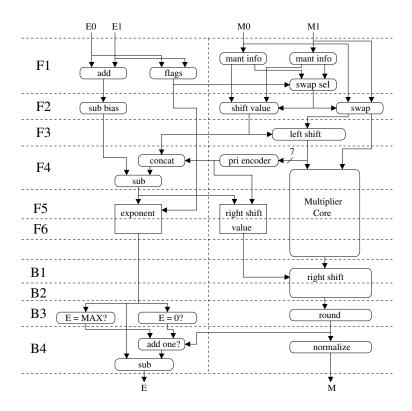

The double precision multiplier is divided into 10 operational stages<sup>2</sup>. In addition, there is a fixed point multiply core which multiplies the two mantissas together. The total latency of the unit depends on the latency of the multiplier core. For Virtex2Pro, the multiplier core uses block multipliers and requires 4 cyles, resulting in a total latency of 12 cyles for the floating-point multiply. In Virtex4, the core uses DSP48 blocks, which include arithmetic logic in addition to the multiplier. These blocks reduce the required logic, but increase the latency to 7, bringing the total latency to 15.

Figure 3.3 shows the general breakdown of the stages for the multiplier. The mantissas are prepared for the multiplier core in the first three stages. This includes unpacking the numbers, checking for IEEE special values and normalizing a denormal input. The normalization logic includes an optimization which dramatically reduces the size of the unit: A denormal number is not fully normalized. Instead, the last three stages of shifting (4, 2, and 1) are removed to save logic. The result is that the backend shift path must be wider. However, the net result is a reduction of logic. The multiplier core begins operation in stage F4, and the backend stages (B1 through B4) round the result and prepare the mantissa for repacking into the IEEE format. The exponent path begins in stage F1 and runs through stage F6. Stages F4 through F6 operate in parallel with the multiplier core. The front-end stages add the two exponents together, subtract the bias and subtract the amount that the mantissa was shifted. In addition, the exponent is adjusted based on any IEEE special values. This result is then passed to the back end which will adjust it for the case of overflow, or in the case where the result of the core is greater than or equal to 2 and the mantissa must be shifted back into the acceptable range.

<sup>&</sup>lt;sup>2</sup>There are two versions of the multiplier: one which supports denormal numbers and one which doesn't. The unit described here provides full support for denormal numbers.

**Figure 3.3.** General computation layout for the floating-point multiplier

### **Characteristics**

To access the quality of the Sandia floating-point modules, we have compared the performance characteristics of the floating-point units created in this project to those from Xilinx, Inc., which is currently the next best library available, in terms of performance.

The data shown in Table 3.3 gives the latency, size and speed characteristics of floating-point adders and multipliers found in the Sandia and Xilinx floating-point libraries. To make the comparison as accurate as possible, the units were configured to be as much alike as possible. This means that the Sandia units have removed denormal support and discounted the initial registers in both the size and latency fields. Also, the Xilinx double precision multiplier was created using the "medium usage" option so that it used the same number (9) of DSP blocks as the Sandia multiplier.

The Sandia floating-point units were mapped to Xilinx Virtex4 parts with a speed grade of -11. Sizes and speeds for each unit were obtained by placing a single unit in each FPGA and using the Xilinx place and route tools (ISE 8.1.03i) to determine size and maximum operating frequency. The numbers for the Xilinx library where found in the Xilinx Floating-Point Operator v2.0 datasheet. However, attempts to validate these numbers using the same methodology used for the Sandia units suggest that the Xilinx units are 20% larger than reported in the data sheets. This discrepancy arises because the datasheet numbers are determined setting the pack factor to one (-c 1). which constrains the tools to map and place the design into 1% of the FPGA area, if possible. This option is unlikely to be useful for a real application because of the clock rate penalty incurred. The table presents two numbers for the size of the Xilinx units: first, numbers directly from the data sheet (denoted Xilinx DS) and second, sizes from actual runs (denoted Xilinx) using the default pack factor. For double precision units, the Sandia adder provides a 1.7X size benefit while maintaining the same clock frequency and a 25% decrease in latency. The Sandia multiplier is about one-third the size of the Xilinx multiplier, operates at the same frequency and provides a 40% reduction in latency.

**Table 3.3.** Floating-point Unit Characteristics (size in slices, latency in cycles and speed in MHz)

| Single Precision on Virtex4 (-11 speed grade) |               |     |       |            |     |       |  |

|-----------------------------------------------|---------------|-----|-------|------------|-----|-------|--|

| Library                                       | Adder         |     |       | Multiplier |     |       |  |

| -                                             | Size          | Lat | Speed | Size       | Lat | Speed |  |

| Sandia                                        | 296           | 9   | 360   | 145        | 9   | 319   |  |

| Xilinx                                        | 428           | 11  | 377   | 159        | 9   | 396   |  |

| Xilinx DS                                     | 329           | 11  | 377   | 119        | 9   | 396   |  |

| Double Precision on Virtex4 (-11 speed grade) |               |     |       |            |     |       |  |

| Library                                       | Library Adder |     |       | Multiplier |     |       |  |

|                                               | Size          | Lat | Speed | Size       | Lat | Speed |  |

| Sandia                                        | 507           | 9   | 275   | 384        | 10  | 274   |  |

| Xilinx                                        | 860           | 12  | 271   | 1181       | 17  | 267   |  |

| Xilinx DS                                     | 692           | 12  | 271   | 864        | 17  | 267   |  |

## Chapter 4

## Implications of Trends in FPGA Performance

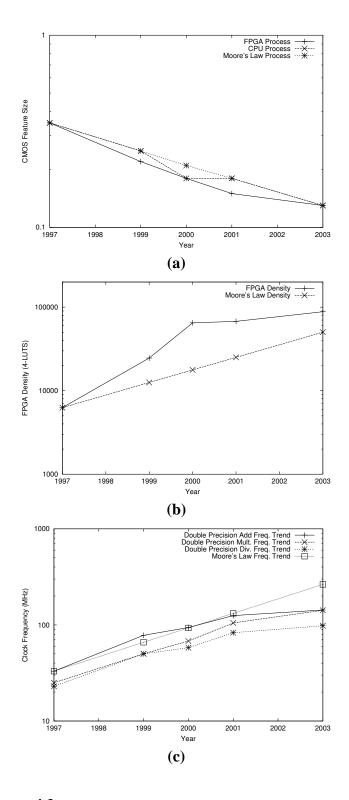

As a precursor to the project in New Mexico, we studied trends in the performance of FP-GAs and FPGA systems. We present the results of that study here for background, along with a retrospective on changes in those trends. To explore the potential of FPGAs to deliver their high peak performance to scientific applications, we also explored several important computational kernels. In this section, we focus on cycle accurate simulations of the performance of several kernels. We include a discussion of details such as memory bandwidth requirements and the parallelism required within the kernel. Leveraging data from our analysis of the trends in FPGA performance, the performance of the kernels was extrapolated to future systems and requirements, such as memory bandwidth, were extrapolated based on future performance levels.

### Trends in FPGA Performance

Trends in the floating-point performance of FPGAs were analyzed immediately before the start of these FPGA projects[37]. The primary results from that work are provided here to illustrate the potential of FPGAs in the domain of scientific computing. Included after the 2003 analysis is a retrospective which discusses how these trends have held up over the last 3 years.

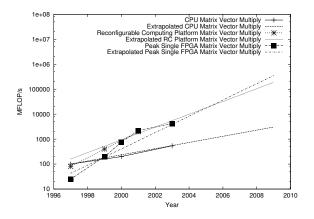

Peak floating-point performance for both microprocessors and FPGAs is analyzed over the period from 1997 to 2003 and extrapolated from there. For the microprocessor, performance is doubled every 18 months to represent the well known corollary of Moore's law. The trend line is forced through the 2003 data point for microprocessors. Since no such corollary has been established for FPGAs, the trend line is derived by starting with the 1997 data point, selecting a very conservative fit, and rounding the slope down.

Table 4.1 lists the parts chosen for the performance comparison. The commodity microprocessor with the highest peak performance was chosen for each of three years (regardless of the release date during the year). Since microprocessor performance trends are well known, only three data points were deemed necessary. Similarly, five FPGAs were chosen

**Table 4.1.** Parts used for performance comparison

| Year | FPGA                | CPU               |

|------|---------------------|-------------------|

| 1997 | XC4085XLA-09        | Pentium 266 MHz   |

| 1999 | Virtex 1000-5       |                   |

| 2000 | Virtex-E 3200-7     | Athlon 1.2 GHz    |

| 2001 | Virtex-II 6000-5    |                   |

| 2003 | Virtex-II Pro 100-6 | Pentium-4 3.2 GHz |

for data points over the course of the same 6 years. An effort was made to choose the largest, fastest speed grade part with reasonable availability during that year<sup>1</sup>. For 2001, a stepping 0 Virtex-II 6000-5 device was chosen. Device stepping 1 was released early the next year and significantly improved the embedded multiplier performance. The part chosen for 1997 was chosen to be as representative as possible of the devices that would have been available; however, there was a constraint on which devices could be placed and routed for these experiments. The oldest tools that were available were Xilinx 4.2i, which do not support parts older than the XC4000XLA series. The XC4085XL-2 might have been a better choice, but the tools available would not target that device.

Admittedly, there are limitations to this type of analysis; however, the conservative assumptions that were made and the dramatic performance improvements projected should compensate for such limitations so that the "answer" is unchanged. For example, the order of magnitude performance advantage in 2009 may carry the same cost premium as current large devices. However, cheaper members of the same FPGA family will likely achieve a cost and performance advantage since FPGA performance is typically linear within a family, but cost is almost exponential. A second limitation is the lack of accounting for structures such as address generation and integer computation units. Such units are typically very simple in an FPGA. Finally, integration into a system is not considered here.

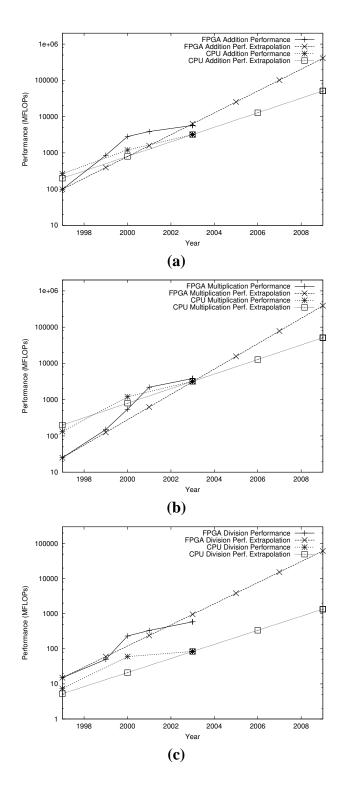

### Addition

Figure 4.1 (a) indicates that FPGAs have significantly higher floating-point addition performance than commodity CPUs. This is a surprising revelation since FPGAs are generally considered to provide poor floating-point performance at best. More surprising still is the fact that FPGAs have been ahead for almost four years. The trend line for floating-point addition on FPGAs projects a growth rate of  $4\times$  every two years. This trend line is diverging from the performance trend line for CPUs, which is only  $2\times$  every 18 months. Notably, double precision addition performance on CPUs has been growing slower than the trend line from 1997 to 2003.

<sup>&</sup>lt;sup>1</sup>These selections were made based on input from Chuck Cremer at Quatra Associates, Jason Moore at Xilinx, and personal memory.

FPGAs achieve this significant advantage over CPUs because their resources are configurable. If an application requires a very addition rich mixture of instructions, the FPGA can provide that. In contrast, commodity CPUs have a fixed allocation of resources that can be successful for a well mixed instruction stream, but has significant limitations in code that is dominated by one instruction.

### Multiplication

FPGAs have not dominated CPUs in floating-point multiplication performance for nearly as long they have in floating-point addition performance. Figure 4.1(b) indicates that FPGAs have only exceeded CPUs in multiplication performance since 2001 for double precision arithmetic. However, the trend lines are diverging more rapidly with multiplication performance growing at an average rate of  $5\times$  per year from 1997 to 2003. This is primarily because of the addition of  $18\times18$  fixed multipliers in the Virtex2 series of parts. The use of these components to implement the multiply of the mantissas (9 for double precision, 4 for single precision) dramatically reduced the area required. This trend is likely to continue since architectural improvements (notably faster, wider, fixed multipliers) are likely to continue.

The CPU performance in Figure 4.1 (b) has grown slightly faster than the Moore's law trend line between 1997 and 2003. For double precision, this is primarily because of a change between 1997 and 2000 to allow multiplies to issue every cycle.

### **Division**

As seen in Figures 4.1 (c), FPGAs have long exceeded CPUs in floating-point division performance — with one minor caveat. An XC4085XLA is not big enough (by a significant margin) to implement a double precision divider. Thus, the "performance" of a double precision divider on that part is the fraction of the divider it can implement times the estimated clock rate. This explains why the 4× trend line overestimates the performance of the 2003 part: components that can implement the operation are constrained to integer multiples of divide units. The XC4085XLA had a second artificial performance inflation because the mapper packed the CLBs much tighter to try (in vain) to make it fit. Thus, the area estimate is significantly smaller than it would otherwise be.

Commodity microprocessors are not well optimized for divide operations. This is a significant issue for some scientific applications[39]. Slow divides have first and second order effects: the division instructions are slow (and unpipelined) and these slow instructions clog the issue queue for modern microprocessors. This makes divide rich applications a good target for FPGA implementations.

**Figure 4.1.** Floating-point performance for: (a) double precision addition, (b) double precision multiplication, and (c) double precision division.

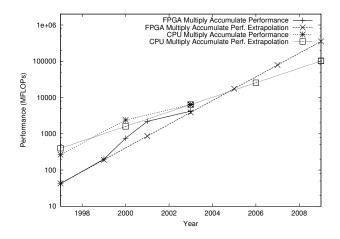

**Figure 4.2.** Floating-point double precision multiply accumulate performance

### **Multiply Accumulate**

Multiply accumulate is somewhat different from the other operations considered in that it is a composite operation. More importantly, it is a composite operation that is fundamental to a number of matrix operations (including LINPACK). Figure 4.2 indicates that FPGAs are still somewhat slower than CPUs at performing this operation. FPGAs are, however, improving at a rate of  $4.5\times$  every two years. This improvement rate (effectively a composite of the performance improvements in addition and multiplication) yields a significant win for FPGAs by the end of the decade.

It would be easy to suggest that the comparison between FPGA and CPU in this case is not "fair" because the FPGA requires many concurrent multiply accumulates (in one multiply accumulate functional unit) to overcome the latency of the adder and achieve the projected performance; however, it should be noted that the Pentium-4 must alternate issuing two adds and two multiplies<sup>2</sup> with 4 cycle and 6 cycle latency, respectively, to achieve its peak performance [1]. With the small register set in the IA-32 ISA, this is not necessarily easier to exploit than the concurrency and parallelism available on the FPGA.

### **Analysis**

A common theme among the performance graphs is the flattening of the performance trend line from 2000 to 2003. This is supported by the data in Figure 4.3, which clearly indicates a flattening in the growth of area, increase in clock rate, and feature size reduction. This

<sup>&</sup>lt;sup>2</sup>The throughput of the SSE2 multiplier is one instruction per 2 cycles. Each instruction can do two multiplies.

**Figure 4.3.** Basic FPGA property trends including: **(a)** CMOS Feature size, **(b)** density in 4-LUTs, and **(c)** clock rate.

appears to bode ill for the projected performance trends; however, a closer look at Figure 4.3 indicates differently. In Figure 4.3(a), the trend in FPGA feature size broke sharply between 2001 and 2003, but it is still on the same overall trend line for the 6 year period as CPUs. Indeed, low cost FPGAs have already been introduced on the 90 nm process — well ahead of CPUs. High performance parts are expected to be introduced next year concurrently with CPUs based on 90 nm technology. Similarly, Figure 4.3(b) shows that the pace of FPGA density improvements has dropped sharply from 2000 to 2003, but overall density increases are still above the Moore's law projection. Even if a much larger device (the XC40125EX) was used as the 1997 baseline, the overall density improvement would remain slightly above the Moore's law projection.

Figure 4.3(c) seems to tell a slightly different story with regards to clock rate. The "Moore's law" trend line for clock rate provides a reference that clearly indicates that clock rate has not scaled as expected. However, this seeming discrepancy is relatively easy to explain. The device used as representative of 1997 technology for these experiments was the XC4085XLA-09. A more accurate part would have been the XC4085XL-2, but the Xilinx 4.2i tools that were available for these experiments would not process such a device. A XC4085XL-2 part is approximately 40% slower than the XC4085XLA-09 part used. Combining this with the significant performance increase that Virtex-II Pro parts should receive as the tool chain develops trends in clock rates that meet the expectations of Moore's law.

Improvement in addition and division performance are derived strictly from technology improvement; however, the  $5\times$  every two years performance growth of multipliers will be difficult to maintain indefinitely. Fortunately, only minor improvements are needed each generation to realize this gain. This should be readily achievable through 2009 (wider embedded multipliers, enhanced support for shifting, etc.).

# **Analysis Retrospective**

FPGA vendors have not continued to deliver the level of performance improvements projected by the analysis here. While many would attribute this to a slowing in clock rate improvements delivered by Moore's Law, the reality is more closely related to choices made by the FPGA vendors. The primary *computational* market for FPGAs is driven by digital signal processing (DSP) style operations. DSP operations are typically narrow bit widths and, consequently, shallow pipelines. In contrast, floating-point uses both narrow and wide datapaths and has very deep pipelines. Similarly, FPGA vendors have chosen to create product mixes that target a set of domains that do not map well to floating-point applications. The primary concern is the lack of sufficient numbers of DSP48 blocks which limits the number of floating-point multipliers that can be built. If FPGA vendors chose to focus on the HPC market, they could continue to deliver improvements in clock rate for floating-point operations for a few more generations. This could be done both with basic architectural changes and with providing a better optimized set of resources. The latest Xilinx FPGA family, the Virtex5, shows some promise in the direction of architec-

tural enhancements. The Virtex5 provides wider multiplier blocks (though not as wide as we would like to see), it also has attempted to increase clock frequency by moving from 4-input LUTs to 6-input LUTs, and by providing a coarser grained carry chain. However, it is unclear if Xilinx will provide a part with a good mix of these components (this only family currently released does not have a good mix of logic to multipliers).

The story with microprocessors is more complex. While microprocessors had been falling off of the trend of doubling performance every 18 months, recent developments, such as the move to 4 FLOPs per clock, have suggested that the microprocessor vendors are again looking to architectural changes for performance. These changes are likely driven by the perception of competition from the accelerator market, and have even led Intel to announce a prototype "teraFLOP on a chip". These types of advances could significantly erode many of the advantages an FPGA may have; however, the microprocessor market is *not* currently expanding memory bandwidth, so FPGAs could still deliver a significant advantage in *sustained* performance.

# **Kernels Explored in Simulation**

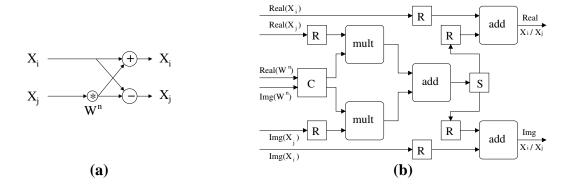

We explored four kernels in cycle accurate hardware description language (HDL) level simulation. These included three basic linear algebra subroutines (BLAS): a matrix-matrix multiply (DGEMM), a matrix-vector multiply (DGEMV), and a dot product (DDOT). We also explored the fast Fourier transform (FFT). Here, we present results from DGEMM, DGEMV, and FFT as they represent three unique points in the spectrum.

Matrix multiply (DGEMM) is a completely computationally bound code in the sizes that most people study. Because it performs  $N^3$  operations over  $N^2$  data with numerous independent operations, it is highly amenable to sustaining high levels of performance on both FPGAs and microprocessors. In contrast, a matrix-vector multiply (DGEMV) requires as many memory operations as floating-point operations. This is much more representative of many codes at Sandia (an iterative solver, for example). Finally, the FFT operation has a much more complex control flow and more data dependencies than either DGEMM or DGEMV operations. Thus, the three kernels we present here highlight three unique facets of how FPGAs behave on floating-point operations.

# **Matrix Multiply**

The standard matrix multiply (the DGEMM BLAS routine) is defined as:

$$\mathbf{C}_{ij} = \sum_{k=0}^{N-1} \mathbf{A}_{ik} \mathbf{B}_{kj} + \mathbf{C}_{ij}$$

(4.1)

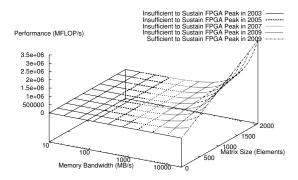

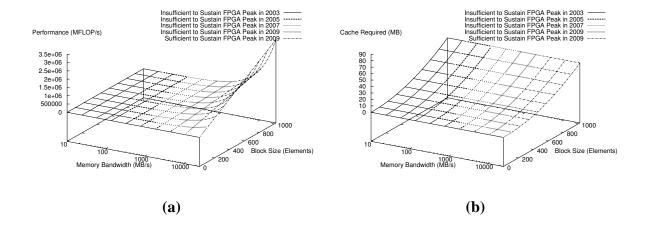

**Figure 4.4.** Maximum achievable performance versus memory bandwidth and matrix size

In the best case, this requires  $4N^2$  memory accesses<sup>3</sup> and performs  $2N^3$  floating-point operations. This yields  $\frac{N}{2}$  floating-point operations for each element retrieved from memory. Achieving the best case, however, imposes the unrealistic requirement that two matrices be cached in the processor. Fortunately, proper use of caching in modern processors allows them to sustain a high percentage of peak with relatively low memory bandwidth. If each matrix only had to be retrieved from memory once, the maximum sustainable floating-point rate would be:

$$FLOPs = \frac{\frac{N}{2} \times BW}{8} \tag{4.2}$$

where BW is the memory bandwidth in bytes per second, N is the dimension of the matrix, and 8 bytes are required to store a floating-point number. This is graphed in Figure 4.4 on a log-log graph.

Typically, however, the processor cannot store all of the matrices involved. Instead, some form of blocking is used to divide the matrix into smaller pieces[42]. These smaller pieces are loaded into the processor, the computations are performed on them, and the partial results stored. For example, for a  $64 \times 64$  matrix multiply, each matrix might be broken into 64 regions that are  $8 \times 8$ . A row of these blocks would then be multiplied by a column of these blocks to create an  $8 \times 8$  block of the result. In the process, the partial result (an  $8 \times 8$  block) would be updated 8 times (although typically in local storage or cache). The ultimate result is that the matrices are fetched several times more than would otherwise be necessary. For blocks of dimension S, this yields a factor of  $\frac{N}{S}$  increase in accesses to the A and B matrices, leading to  $2N^2 + \frac{2N^3}{S}$  memory accesses. For large matrices, this approaches

<sup>&</sup>lt;sup>3</sup>This assumes square matrices and includes retrieving three matrices and storing one matrix.

Figure 4.5. Matrix multiply implementation

a floating-point rate of:

$$FLOPs = \frac{S \times BW}{8} \tag{4.3}$$

### **FPGA Implementation**

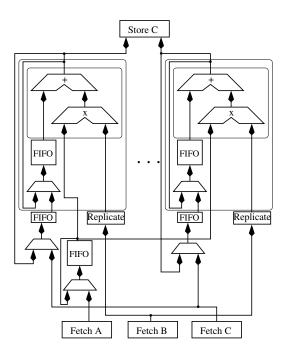

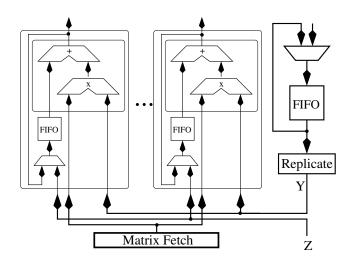

One way to view matrix multiplication is as a collection of *N* matrix-vector multiplications. As such, it exhibits significantly more parallelism. Unfortunately, it is impractical to store all of a matrix in most modern devices (with the possible exception of the Itanium chips with the largest caches) for reasonable matrix sizes. Thus, the implementation chosen (shown in Figure 4.5) resembles a collection of matrix-vector multiplications, but blocks the matrix to reduce total storage requirements.

To perform the matrix multiplication, a  $S \times \frac{S}{m}$  section of a block of the matrix **B** in column major order is loaded into each of m MACC units. Simultaneously, the matching block of the matrix **C** is also loaded into the MACC unit in column major order. This requires a total of  $6S^2$  elements of storage at 8 bytes per element. The corresponding block of **A** is loaded into a FIFO that is used to broadcast it to all MACC units  $\frac{S}{m}$  times (also in column major order). Each MACC unit creates S replicas of each element of **B** to match the number of rows of **A** that will be multiplied with it. This provides the concurrency needed to hide all

**Figure 4.6.** A comparison of double precision floating-point matrix multiplication performance on CPUs, FPGAs, and RC platforms

of the latency of the adder. As each element of **B** and **C** is used, it is discarded. When the MACC unit finishes, it produces an intermediate version of the result **C**. This intermediate is fed back to the input to be added to the multiplication of the next pair of blocks from **A** and **B**. When the final version of a block of **C** is produced, it is stored. Overall, this requires no more than  $6S^2$  elements of storage at 8 bytes per element. This includes 2 copies of each matrix block — one to operate on and one to change it from row major to column major order.

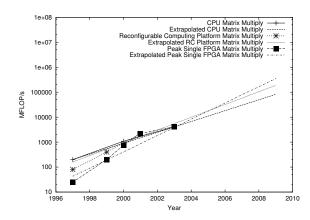

# **Performance Comparisons**

Matrix multiply is not typically memory bound. With relatively little caching, modern microprocessors can achieve a high percentage of peak performance with commodity memory attached. As seen in Figure 4.6, this enables microprocessors to maintain an edge over FP-GAs and RC platforms up through 2003. For this graph, data points for the CPUs in 2000 and 2003 were measured and the data point for the CPU in 1997 was taken from [41]. The extrapolated trend line projects a  $4.5 \times$  growth in performance every 3 years.

Like microprocessors, the performance of matrix multiply on FPGAs is unconstrained by any architectural features. As such, the rate of growth (4.5× every two years) is the same as for the multiply-add performance projected in [37]. Recent reconfigurable computing platforms are also included in this comparison. These platforms often use multiple FPGAs and provide a "realistic" design point with a "realistic" memory bandwidth.<sup>4</sup> Most points are estimated, but an implementation on the Osiris board to validate the estimates has been simulated. Extrapolating the trend yields a performance growth rate of 3.25× every two

<sup>&</sup>lt;sup>4</sup>Realistic in that people buy it, but not realistic in a cost comparison with traditional processors.

years. This is lower than the FPGA growth rate because the number of FPGAs on RC platforms has been steadily decreasing. This growth rate may accelerate over the coming years (since less than one chip per board is unlikely).

Reconfigurable computing platforms also demonstrate the same characteristics (peak performance and performance growth) as matrix-vector multiply. Again, all but one of these points are currently estimated, but an implementation has validated one data point on an Osiris board.

# **Memory Requirements**

The key feature that distinguishes matrix multiplication from matrix-vector multiplication is that it requires much less memory bandwidth to maintain peak performance. This is an important factor since supercomputing applications of FPGAs are unlikely to provide the level of memory bandwidth that many RC platforms provide (due to the additional cost and negative reliability implications of several extra banks of memory). As such, it is important to examine the storage needs of FPGAs relative to their peak bandwidth and peak performance.

Figure 4.7(a) illustrates the high levels of performance achievable with relatively little memory bandwidth and sufficient internal storage. For example, the 4 GFLOP/s of peak floating-point capability available in 2003 can be sustained with only 512 MB/s of memory bandwidth and only 192 KB of internal storage in the FPGA. This easily falls within the limits of even the Virtex-II family. The important observation here is that internal memory can be traded for external memory bandwidth.

The flip side of this analysis is to consider the amount of internal memory needed for various memory bandwidth and block size combinations. Figure 4.7(b) compares the size of the internal cache needed to the amount of memory bandwidth needed and the block size. By 2009, FPGA platforms will need to provide several gigabytes per second of memory bandwidth or several megabytes of internal storage. For this algorithm, however, both the memory bandwidth and internal storage needed to maintain peak performance appear to be easily achievable.

An interesting revelation from this analysis is the significant gains in efficiency that FP-GAs achieve. These gains appear to arise from the ability to explicitly manage internal storage and the high aggregate internal memory bandwidth. Commodity processors typically achieve only 80-90% of their peak performance on dense matrix multiplies while requiring hundreds of kilobytes of cache and gigabytes per second of memory bandwidth. By contrast, the FPGA only requires 192 KB of storage and 512 MB/s of external memory bandwidth. If this trend holds for other algorithms, it will be a significant advantage for FPGAs in the realm of high performance computing.

**Figure 4.7.** (a) Maximum achievable performance versus memory bandwidth and block size; (b) Memory needed in an FPGA to maintain peak performance versus memory bandwidth and block size

# **Matrix-Vector Multiply**

The DGEMV BLAS routine is defined as:

$$\mathbf{w}_i = \sum_{j=0}^{N-1} \mathbf{A}_{ij} \mathbf{y}_j + \mathbf{z}_j \tag{4.4}$$

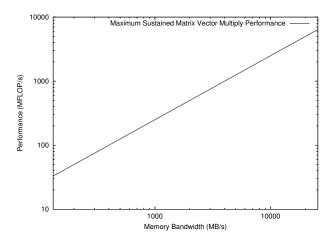

The lower bound on memory accesses is  $N^2 + 3N$  (it must retrieve a matrix and two vectors and store one vector) and performs  $2N^2$  floating-point operations. Achieving that requires that the vector be cached in the processor. In the limit, two floating-point operations are performed for each element retrieved from memory. DGEMV is also a memory limited operation on microprocessors. The maximum sustainable floating-point rate is:

$$FLOPs = \frac{2 \times BW}{8} \tag{4.5}$$

where BW is the memory bandwidth in bytes per second and 8 bytes are required to store a floating-point number. This is graphed in Figure 4.8 on a log-log graph.

### **FPGA Implementation**

Matrix-vector multiplication has somewhat less inherent parallelism than matrix multiply. When the matrix dimension is greater than the depth of the addition pipeline, it is possible

**Figure 4.8.** Maximum sustainable matrix vector multiply performance versus memory bandwidth

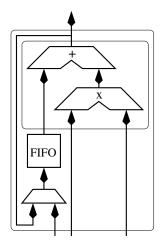

to use all of the floating-point capabilities of the FPGA without making special adaptations to the multiply accumulate unit. Instead, a standard MACC (shown in Figure 4.9) is used with additional storage and control outside of it as shown in Figure 4.10.

The design in Figure 4.10 assumes that the matrix,  $\bf A$ , is stored in one logical memory with a bandwidth that will support some number of MACC units, m. Thus, the vectors  $\bf y$  and  $\bf z$  are loaded and broadcast to all of the MACC units while the matrix is fetched from memory and distributed to the MACC units. Before broadcasting to the MACC units, each element of  $\bf y$  is replicated k times (where k is the pipeline depth of the adder). Effectively, there are k rows of the matrix being multiplied with the vector in each MACC unit. The vector  $\bf z$  is used to initialize the summation unit. Thus, one MACC unit is fed the  $j^{th}$  element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k element of k rows to match k copies of the k rows to match k copies of the k rows to match k rows to

The limitation of this approach is the need to store a vector for large values of N. The alternative is to divide the vector into parts of length L and perform the equivalent of  $\frac{N}{L}$  smaller matrix-vector multiplies. The first would add the vector  $\mathbf{z}$  to the result (as in Equation 4.4) and subsequent portions of the operation would add the intermediate result in place of  $\mathbf{z}$ . This would increase the number of memory accesses to  $N^2 + \frac{3N^2}{L}$ . For FPGAs from 1999 and forward, an L value of 2000 is achievable. Thus, the  $N^2$  term for the matrix access still dominates. This issue would only serve to decrease performance estimates for earlier FPGAs (thus skewing the trend line) and will not be considered further.

Figure 4.9. Multiply-accumulate unit

Figure 4.10. Matrix vector multiplication implementation

**Figure 4.11.** A comparison of double precision floating-point matrix-vector multiplication performance on CPUs, FPGAs, and RC platforms

### **Performance Comparisons**

Unlike matrix multiply, matrix-vector multiplication is typically a memory bound operation; however, devices that provide enough memory bandwidth shift the limitation to the floating-point performance of the device. The performance of recent RC platforms is compared with recent commodity CPUs and the peak performance possible with a single FPGA in Figure 4.11. CPU performance was measured for the 2000 and 2003 data points with an N of  $1000^5$  and estimated for the 1997 data point based on the differences in memory bandwidth and architecture.<sup>6</sup>

Like DGEMM, peak DGEMV for the FPGAs is based on the maximum multiply accumulate performance of the FPGA. This is because the use of all of the FPGA pins for memory provides abundant bandwidth to achieve the peak performance. DGEMV also has sufficient independent parallelism to enable the FPGA to achieve its full peak performance on smaller matrix and vector sizes. Extrapolating this trend yields the same  $4.5 \times$  growth every two years as the dot product since the FPGA pin bandwidth never becomes the limiting factor.